您当前的位置:检测资讯 > 科研开发

嘉峪检测网 2022-03-28 22:35

1. 芯片设计公司研发实验室的工作内容简介:

芯片设计公司一般都有自己的芯片研发实验室,主要为公司的芯片进行各种验证测试,包括芯片自身的性能测试、芯片在各种电子终端产品上应用的仿真测试,以及向芯片客户提供芯片的失效分析等技术支持。

芯片研发实验室里的设施主要包括进行芯片测试的工作台、测试设备以及电子维修的工位。

2. 芯片研发实验室会有高静电的情形么?

芯片研发实验室里的工作相比于电子工厂的生产线,自动化程度非常低,各种测试项目基本全部靠工程师手动操作来完成各种测试平台的搭建、调试等。

芯片设计公司的每个工程师基本都要负责数个工位的测试项目,由此,工程师在实验室里工位上以及工位间的走动就会很频繁,这样,工程师人体上的静电(如果不做特别针对性的控制)时常就会很高。

表1,几种常见的人员活动中的人体静电带电行业调查数据

实验室的环境湿度对实验室内工程师的走动及各种手动操作(测试连接插装与拆解)的静电带电有着直接的影响。以华南地区的广州、深圳等地的一年环境湿度统计结果而言,每年一般都会在12月前后10多天的相对湿度降至20% RH左右。据此可以推断,国内几乎全部地区每年都会有中低湿情况致使实验室内的静电会比较高。

3. 静电会给芯片研发实验室的测试造成什么影响?

静电是如何对芯片构成危害的,参见前述的文章《概说静电对微电子产业的影响》。

一是工程师人体上的静电,在工程师走到各测试工位上操作测试平台时(尤其是靠近或接触测试平台的电气管脚部位),就构成了典型的人体静电放电情形。生活中,每个人都有冬天里触摸金属门把手或车门被静电电击的多次体验。而对于测试平台上的各类芯片(包括芯片公司的产品),在人体静电完全不受控的工程师手部触摸到其电气管脚时,势必会产生很高强度的放电电流。这种强放电电流,一方面可能直接导致测试平台上的电子元件失效,同时,另一方面也会对进行中的测试产生显著的干扰(也就给芯片的测试结果带来干扰,这一方面反而是芯片验证测试更为关注的)。

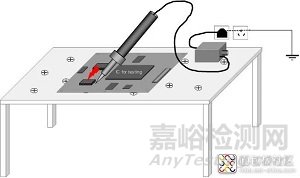

图1,芯片研发实验室测试工位工程师人体静电操作测试平台的静电放电原型

二是测试工位中的高静电源带来的影响。以工位的台面为例,如果选用一般的塑胶质表面,则在低于55%RH中低湿的环境条件下,工位的台面上就会时常出现高静电带电的情形。

图2,高静电工作台面上操作芯片测试平台连接插拔过程的静电放电风险原型-芯片测试电路板对测试设备发生静电放电

图3,高静电工作台面上芯片测试电路板焊接维修过程的静电放电原型-芯片测试电路板对接地的电烙铁放电

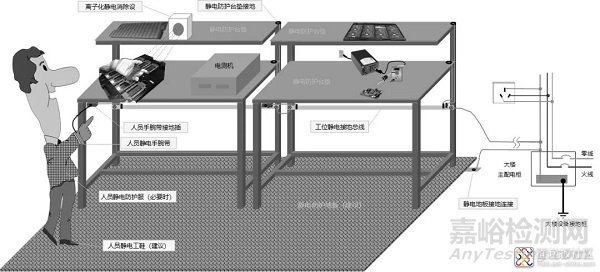

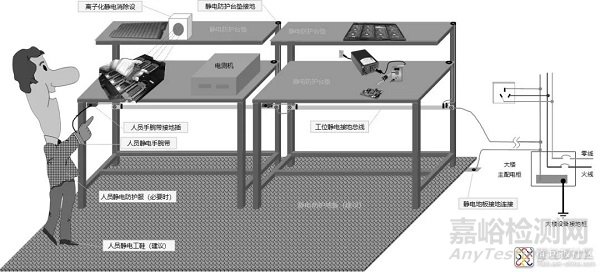

4. 芯片研发实验室的静电防护方案

基于芯片研发实验室的主要静电来源与高静电风险的操作,针对性的静电防护方案主要包括三部分:

一是实验室内工程师的人体静电必须采取有效的控制措施,可以采用静电手腕带接地系统(首选),也可以辅助采用静电鞋_静电地板系统(可靠性与可行性相对较差)。

二是实验室内各测试工位的工作台面,应避免采用绝缘材质(容易产生并累积高静电),可采用铺装静电防护台垫,实现静电防护工作台面,这样就消除了测试工位中最主要的静电来源。

三是个别工位采取特定的静电防护措施。例如,测试平台中涉及到操作大尺寸的绝缘部件(塑胶外壳、膜材等),就需要加装离子化措施,来中和消除这些物料操作过程产生的高静电。

综上所述,芯片研发实验室各工位的静电防护措施,主要包括以下部分:

1) 工位的静电接地系统,供工位的静电防护台垫、人体手腕带系统以及静电地板进行接地连接。静电主地首选实验室内合格的电气设备地;

2) 工位的静电防护工作台面,表面电阻<1E9欧姆(特定的测试工位要求台垫表面电阻>1E4 欧姆),具体可参照行业标准ANSI/ESD S20.20或IEC61340-5-1关于静电防护台面的技术性要求;

3) 人体静电接地系统,首先工程师佩戴静电手腕带实现人体接地的做法;

4) 离子化静电中和消除措施,主要针对于工程师操作中易于产生高静电的测试工位。

图4,芯片研发实验室工位的静电防护架设方案

来源:面包板社区