您当前的位置:检测资讯 > 科研开发

嘉峪检测网 2025-08-13 11:10

信号强度与电压源

信号的强度可以通过它与理想电压源的接近程度来衡量。通常,信号越强,它能提供或吸收的电流就越大。电源(VDD)和地(GND)是数字信号中“1”和“0”的来源。

NMOS与PMOS晶体管简介及反相器电路回顾

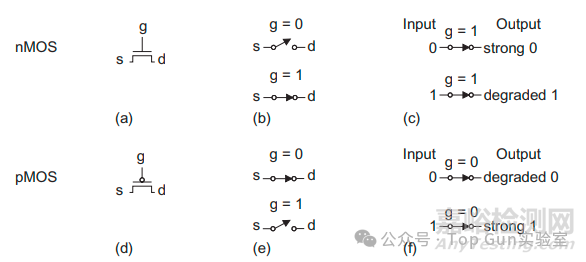

NMOS晶体管几乎是一个完美的开关,当输入为“0”时导通,输出为“0”(强0)。然而,请注意只是"几乎",NMOS晶体管在输入为“1”时表现不完美,高电压水平会略低于VDD,这将在后续文章中详细解释。我们称之为“退化1”或“弱1”。

PMOS晶体管则具有相反的特性,当输入为“0”时导通,输出为“1”(强1),但当输入为“1”时,输出会是“退化0”。

上图总结了晶体管的符号和行为,其中g、s和d分别表示栅极、源极和漏极

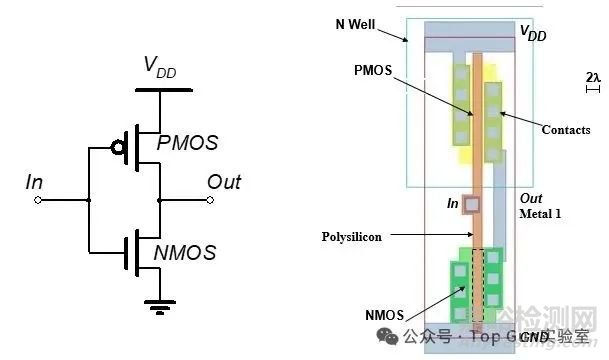

在CMOS逻辑电路中,输入信号通常同时驱动下拉网络中的NMOS晶体管栅极和互补上拉网络中的PMOS晶体管栅极。这种配置确保了NMOS晶体管在导通时能提供稳定的“0”电平,PMOS晶体管在导通时能提供稳定的“1”电平,从而保证输出信号的强驱动能力和电平的无退化。我们将这种特性称为“完全恢复逻辑门”,它显著简化了电路设计,并降低了设计复杂性。下图为典型的CMOS逻辑电路原理图及典型的版图设计,也称为反相器电路。

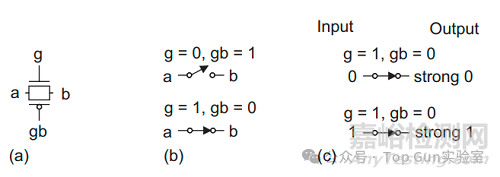

当NMOS或PMOS单独使用时,它们是不完美的开关,我们称之为“传输晶体管”或“直通门”。通过将NMOS和PMOS晶体管并联(下图(a)),我们得到一个当输入为“1”时导通的开关(下图(b)),并且在“0”和“1”两种情况下都能完美导通(下图(c))。我们称之为“传输门”或“直通门”。

在某些电路中,如果只有单个“0”或“1”信号,则可以删除相应的传输晶体管(n管或p管),退化为单个NMOS或PMOS器件。

为什么要用传输门/传输门存在的意义是?

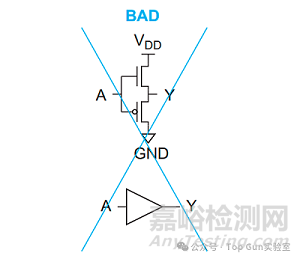

静态CMOS逻辑电路(反相器)设计的输入和输出必须是反相的。当输入为“1”时,NMOS下拉网络导通,输出为“0”;当输入为“0”时,PMOS上拉网络导通,输出为“1”。我们可能会尝试将晶体管倒置以构建非反相门。例如,下图显示了一个非反相缓冲器。为什么在下图打X,因为这种设计存在问题。

虽然这种设计可以使输入输出相同,但是NMOS和PMOS晶体管都会产生退化的输出(详见上文NMOS与PMOS晶体管简介及反相器电路回顾章节描述),因此应避免这种技术。

传输门的功能像一个电子开关, 它可以根据控制信号来选择性地“接通”或“断开”一条信号通路,从而控制输入信号是否能够传递到输出端。 当它“接通”时,输入信号几乎无改变地通过;当它“断开”时,输出端处于高阻态(High-Z),相当于断路。另外,传输门可以双向传输信号,而反相器只能单向传输信号。

总结

简单来说,可以将反相器想象成一个“唱反调”的设备,你给它“1”,它就输出“0”。而传输门则像一个“水龙头”,通过一个开关(控制信号)来决定是让水流(输入信号)通过,还是关掉。

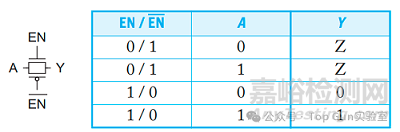

传输门本质上是一个三态电路,它的三个状态是:

导通(ON):当使能信号有效时(例如 EN=1),它像一个闭合的开关,允许输入信号 A 通过,此时输出 Y = A。

截止(OFF)/高阻态(High-Z):当使能信号无效时(例如 EN=0),它像一个断开的开关。此时输出端与输入端断开,呈现高阻抗状态。这就是它的“第三态”。

(注:严格来说,传输门只有导通和高阻态两个由控制信号决定的状态。但因为它能输出高阻态,所以被归类为三态逻辑电路。)

来源:Top Gun实验室