您当前的位置:检测资讯 > 检测案例

嘉峪检测网 2025-09-21 17:38

在半导体那如同星辰般精密的微观世界里,每一次失效都像一桩悬案,考验着工程师们的智慧与洞察力。前文讲到晶圆裂纹检测,今天我们要分享的,就是关于晶圆裂纹的一个真实故障案例。

故障现象:难以捉摸的“隐形杀手”

一切始于一个棘手的漏电问题。按照常规的失效分析(FA)流程,我们对这颗“问题芯片”进行了全面体检。

无损分析未见明显异常:

1.IV测试: 芯片管脚存在漏电和短路的情况。2.外观检查: 完好如初,在显微镜下反复搜寻,也未发现任何典型的裂纹痕迹。3.X-Ray射线检查: 内部结构清晰,没有任何裂纹或空洞的迹象。4.C-SAM声学扫描: 封装良好,未见分层或其他封装缺陷。

所有的初步检查结果都指向“无异常”。然而,芯片的漏电和短路却是铁一般的事实。难道,故障会凭空发生?

水落石出:罪魁祸首终现形

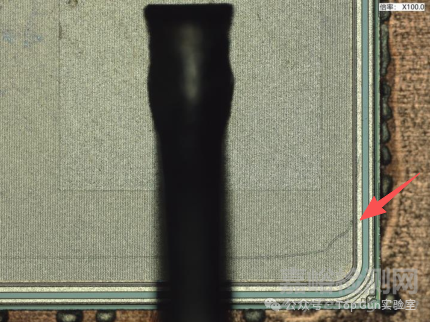

无损分析未发现明显异常,因此分析员决定进行更深层次的破坏性分析。当芯片被化学开盖后,真相终于浮出水面——一道隐蔽的芯片裂纹赫然在目!

这道裂纹,正是导致芯片内部电路短路、引发漏电的直接原因。它像一个潜伏已久的“刺客”,完美避开了所有无损检测手段。同时,开盖后的芯片并未发现明显的EOS Burn Mark,因此可初步排除EOS导致芯片过热烧毁产生裂纹的可能性。

深层思考:探寻裂纹的根源(Root Cause)

找到了直接原因,但对于质量控制而言,更重要的是找到根本原因。

这道裂纹是如何产生的,针对可能性做了罗列:

1.晶圆减薄与切割应力?——晶圆切割(Dicing)的隐匿损伤2.芯片贴装过程中的机械应力?——贴片(Die Attach)过程中的应力集中3.封装过程中的热应力或机械应力?——塑封(Molding)或引线键合(Wire Bond)环节的机械冲击4.还是来自客户端的组装应力?——贴片或PCB板弯曲应力

这道裂纹的形成,很可能是在生产或组装的某个环节,由于潜在的应力过大而埋下的“定时炸弹”。它在初期非常隐蔽,无法被常规手段检测,但在后续的电性或热应力下逐渐扩展,最终导致了芯片的失效。

来源:Top Gun 实验室