您当前的位置:检测资讯 > 科研开发

嘉峪检测网 2025-09-06 18:42

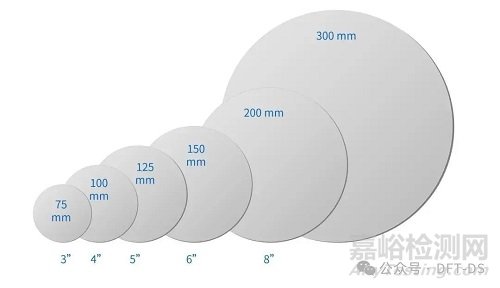

在半导体制造中,晶圆(Wafer)边缘(Edge)的 Die 与中心(Center)的 Die 在性能、良率和可靠性上存在显著差异。这些差异主要源于制造过程中的物理效应、工艺均匀性、热应力和光刻/刻蚀非均匀性等因素。

理解这些差异对于提高芯片良率(Yield)、优化设计规则和进行失效分析至关重要。

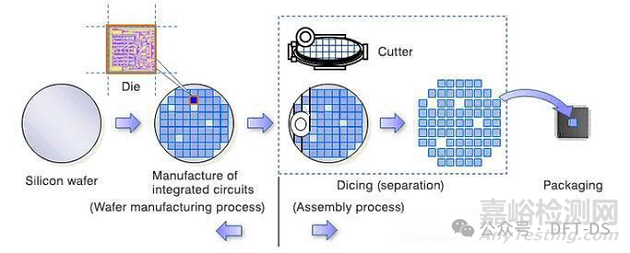

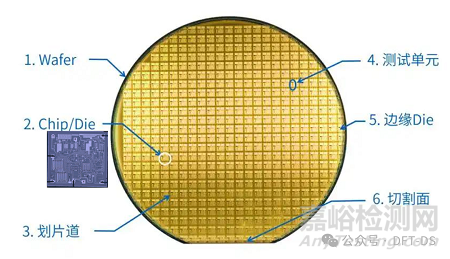

一、什么是 Die?

Die:指晶圆上一个独立的芯片单元(也称“管芯”)。芯片Die(裸片)是半导体制造中的核心概念,指从硅晶圆切割下来的未封装芯片,包含完整的集成电路但未进行封装处理。

一片晶圆上包含数百到数千个 Die。

每个 Die 经过切割、封装后成为独立的芯片。

核心特征

物理形态:裸片是晶圆切割后的独立单元,表面保留切割痕迹,尺寸范围从纳米级到毫米级不等。

与其他术语的区别

Device:指完成封装的芯片成品,强调功能实现。

Chip:泛指所有形态的集成电路,包括封装前后的芯片。

封装状态:未配备外部引脚和外壳保护,仅包含电路结构。

功能定位:作为芯片制造的中间产物,需通过封装测试后才能应用于电子系统。

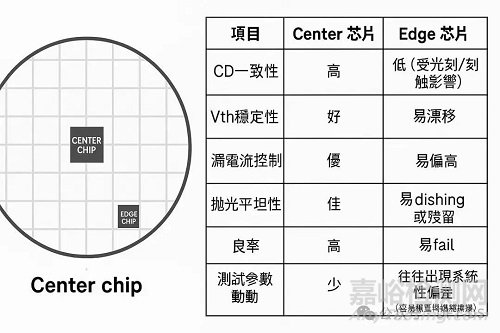

二、Wafer Edge 与 Center Die 的主要差异

|

差异维度 |

中心区域(Center) |

边缘区域(Edge) |

|

工艺均匀性 |

高(光刻、刻蚀、沉积均匀) |

较差(边缘效应导致不均) |

|

良率(Yield) |

高 |

低(通常低5%~20%) |

|

电性参数一致性 |

好(Vt、Id、R、C 稳定) |

差(参数漂移) |

|

热应力 |

小 |

大(边缘散热差,热梯度高) |

|

颗粒污染密度 |

低 |

高(边缘易积聚颗粒) |

|

光刻聚焦(Focus) |

稳定 |

易失焦(晶圆翘曲) |

|

刻蚀/沉积速率 |

均匀 |

边缘速率异常(边缘效应) |

|

机械应力 |

小 |

大(切割时应力集中) |

三、具体差异原因详解

1. 光刻非均匀性(Lithography Non-uniformity)

问题:光刻机在曝光时,晶圆边缘区域容易出现离焦(defocus),因为晶圆可能存在轻微翘曲或边缘厚度变化。

影响:

线宽控制差(CD Uniformity 差)

图案失真(如桥接、开路)

边缘 Die 的晶体管尺寸偏离设计值 → 性能下降或漏电增加

数据:边缘 Die 的关键尺寸(CD)偏差可能比中心高 10–15%。

2. 刻蚀与沉积的边缘效应(Edge Effects)

物理原因:在 CVD、PVD、刻蚀等工艺中,反应气体或离子流在晶圆边缘的分布不均。

表现:

边缘区域沉积层厚度不均

刻蚀速率异常(过刻或欠刻)

金属填充不均 → 电迁移风险增加

例如:铜大马士革工艺中,边缘 Die 的金属线更容易出现空洞或过填充。

3. 热应力与温度梯度

晶圆在高温工艺(如退火、扩散)中,边缘散热更快,导致:

中心温度高,边缘温度低 → 热应力

掺杂分布不均(如硼、磷扩散速率不同)

晶格缺陷增多(如位错)

结果:边缘 Die 的阈值电压(Vt)漂移、载流子迁移率下降。

4. 颗粒污染(Particle Contamination)

晶圆边缘更容易积聚颗粒(来自设备、传输、清洗等)。

颗粒可能导致:

光刻缺陷(如短路、开路)

局部击穿或漏电

统计显示:边缘区域的颗粒密度比中心高 20–30%。

5. 机械应力与切割损伤

在**划片(Dicing)**过程中,锯刀对边缘 Die 产生机械应力。

边缘 Die 更容易出现:

裂纹(Crack)

表面损伤

封装后可靠性下降(如热循环失效)

6. 电性参数漂移(Electrical Parameter Variation)

由于上述工艺不均,边缘 Die 的电性参数通常表现出更大变异:

|

参数 |

边缘 vs 中心 |

|

阈值电压 Vt |

偏移 ±10~20mV |

|

驱动电流 Id |

下降 5~15% |

|

漏电流 Ioff |

增加 20~50% |

|

电阻 R |

增加(金属不均) |

|

电容 C |

变化(介电层厚度不均) |

实测数据:在28nm工艺中,边缘 Die 的漏电平均比中心高 30%,良率低 8–12%。

四、如何缓解边缘效应?

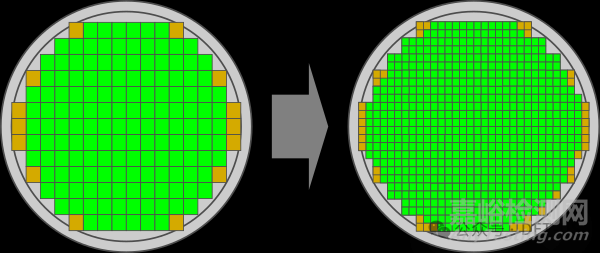

1. 边缘 Die 排除(Edge Exclusion Zone)

定义一个边缘排除区(如 3–5mm),该区域内的 Die 不用于量产。

常见做法:只测试和封装中心区域的 Die。

优点:提高整体良率

缺点:浪费晶圆面积,增加成本

2. 工艺优化

光刻:使用更先进的聚焦控制(如动态调焦)

刻蚀/沉积:优化气体流场,减少边缘效应

热处理:改进炉管温度均匀性

3. 设计补偿(Design for Manufacturing, DFM)

在物理设计阶段,对边缘区域的器件进行尺寸补偿或冗余设计。

使用Guard Ring防止边缘漏电扩散。

4. 测试与筛选

对边缘 Die 进行更严格的参数测试(Parametric Test) 和 老化测试(Burn-in)。

降低边缘 Die 的工作频率或电压,确保可靠性。

五、实际影响案例

|

应用场景 |

影响 |

|

高性能CPU |

边缘 Die 可能无法达到标称频率,降级为低频型号 |

|

存储器(DRAM/NAND) |

边缘坏点增多,需更多冗余修复 |

|

模拟芯片 |

匹配性差,影响ADC/DAC精度 |

|

汽车电子 |

边缘 Die 更易在高温下失效,需严格筛选 |

六、总结

|

项目 |

中心 Die |

边缘 Die |

|

工艺质量 |

高 |

较差 |

|

电性一致性 |

好 |

差 |

|

漏电 |

低 |

高 |

|

良率 |

高 |

低 |

|

可靠性 |

高 |

较低 |

|

成本效益 |

高 |

低 |

结论:

晶圆中心的 Die 质量最优,是高价值芯片的首选区域。

边缘 Die 存在工艺不均、参数漂移、良率低等问题,通常用于低成本或降级产品。

通过边缘排除、工艺优化、DFM设计和严格测试,可有效缓解边缘效应。

在先进工艺(如7nm、5nm)中,由于器件尺寸更小,边缘效应更加显著,因此对边缘控制的要求也更高。掌握这一知识,有助于在芯片设计、测试和量产决策中做出更优选择。

来源:芯片研究室