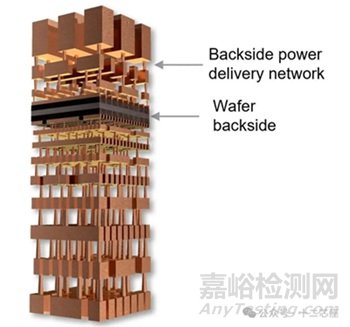

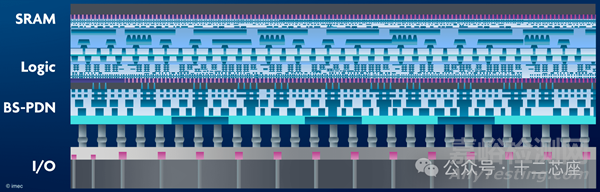

在追求更高性能、更低功耗和更高密度晶体管阵列的竞争中,半导体制造商正在积极拥抱一项名为“背面供电网络”(BSPDN)的根本性架构变革。这项技术将供电从传统的正面(已挤满了逻辑和信号布线)转移到晶圆背面,从而为高密度晶体管逻辑腾出宝贵的空间。

然而,这项革命性的进步带来了全新的套刻和工艺控制挑战,如果处理不当,可能会显著影响良率、成本和上市时间。应用材料公司正在率先推出新一代计量解决方案,旨在利用电子束 (ebeam) 的优势,应对这些新兴挑战。

颠覆性技术带来新的计量挑战

背面功率概念涉及制造互连(称为背面通孔),从晶圆背面穿过硅衬底,直接连接到晶体管级结构(例如源极/漏极)。其主要优势是显著降低电阻、缩短电流路径并提高晶体管密度,所有这些都有助于提升先进逻辑、AI 处理器和下一代移动设备的每瓦性能。

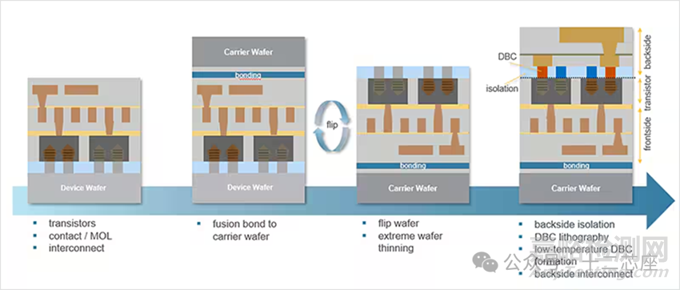

但集成这种新型架构需要复杂的晶圆键合工艺和额外的高精度制造步骤。具体来说,它需要将载体晶圆键合到正面,翻转晶圆,将其减薄至10微米以下的厚度,然后将背面触点图案化并对准先前制造的正面器件层。这些额外的晶圆处理和键合步骤显著增加了叠层工艺的复杂性,并带来了诸多挑战,例如:

键合、减薄和抛光步骤引起的晶圆变形和应力

由于背面加工遮挡了隐藏的正面参考层,导致对准困难

晶圆因图案而变形,产生难以预测和补偿的非线性叠加误差

如果没有精确的覆盖控制,背面通孔和晶体管级结构之间即使出现最轻微的纳米级错位,也会严重影响器件性能、可靠性和产量。

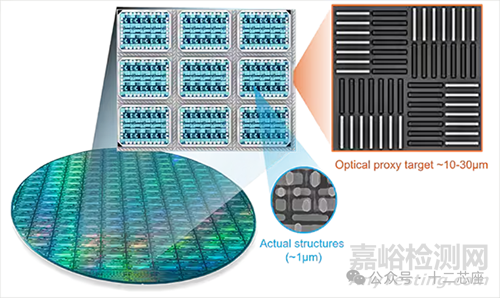

传统的叠加方法已不再足够

历史上,晶圆厂一直依赖于光学套刻测量技术,使用放置在有源器件区域之外的大型替代目标。但随着背面功率的增加,这些目标越来越难以代表实际的器件级套刻。当背面接触直接接触微小的晶体管级特征(例如构成最新环绕栅极晶体管基础的纳米片堆叠)时,这种脱节会变得更加严重。简而言之,传统方法无法可靠地检测出决定最先进节点成败的纳米级套刻误差。

下一代电子束计量技术的需求

为了应对这些前所未有的挑战,晶圆厂迫切需要前所未有的精度、分辨率和效率来测量背面直接接触叠层,以捕捉背面通孔和纳米片之间真实的器件级对准情况。目前的热场发射 (TFE) 设备不足以实现背面功率和 GAA 晶体管架构芯片的大批量生产。业界需要新一代电子束测量技术来实现一系列改进:

更高的分辨率:

需要更高的精度来准确捕捉细微的覆盖偏移和纳米级错位,这对于控制落在复杂堆栈下方的纳米片或栅极结构上的背面接触至关重要。

更高的速度:

变形和所需的校正非常复杂——远远超出了基本的偏移或移位。这需要更大规模的计量,每个晶圆的测量次数将增加10到100倍。更高的速度至关重要,因为计量步骤不能延长。

更高的能量:

下一代量测工具需要以更高的注入能量(高达 60 keV)运行,以便深入穿透复杂的 3D 堆叠。这允许直接测量背面通孔相对于正面晶体管级特征的位置,而无需进行破坏性横截面分析,从而直接提高先进背面功率网络的良率。

更高效地收集背散射电子 (BSE):

先进的 BSE 探测器技术可显著提高收集效率,提供更佳的材料对比度,并更清晰地成像埋层结构。高质量的 BSE 信号能够可靠地检测多层 3D 集成结构中细微的叠层错位。

先进的轮廓提取算法:

为了补充先进的成像功能,下一代工具需要强大的图像增强、降噪和轮廓提取算法。这些先进的软件工具在提升测量精度的同时,克服了电子束引起的充电难题,能够精确地测量纳米片结构上的背面触点——而这正是传统光学工具难以实现的。

应对这些挑战,芯片制造商能够直接测量背面触点与晶体管特征之间的叠对,在制造工艺早期识别晶圆级变形和应力引起的错位,并实现对背面通孔放置的更严格的工艺控制——所有这些都可以显著减少叠对误差,从而对工艺良率产生实际影响。

具有背面供电实现的 3D-SOC 示意图

Process FLOW

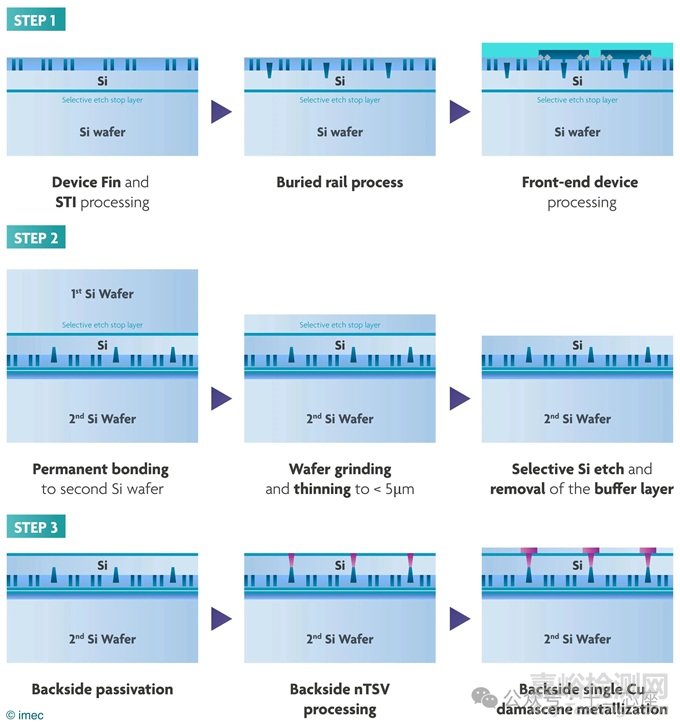

下面,详细阐述BSPDN的具体实现工艺流程,其中nTSV(在极薄的晶圆背面加工)位于BPR之上。例如,在晶圆正面加工的微缩FinFET器件,通过BPR和nTSV连接到晶圆背面。

From: IMEC

步骤 1:采用埋轨进行正面处理

该工艺流程始于在 300 毫米硅晶圆顶部生长一层 SiGe 层。SiGe 层随后作为蚀刻停止层,以结束晶圆减薄(步骤 2)。接下来,在 SiGe 层顶部生长一层薄硅覆盖层:这是制造器件和埋入式电源轨的起点。埋入式电源轨在浅沟槽隔离后定义。在硅覆盖层中蚀刻的沟槽用氧化物衬垫和金属(例如 W 或 Ru)填充。由此产生的埋入式电源轨通常宽度约为 30 纳米,间距约为 100 纳米。然后将金属凹陷并用电介质覆盖。在 BPR 实现后,器件(在本例中为缩放的 FinFET)的加工完成,并且 BPR 通过 VBPR 通孔和 M0A 线连接到晶体管的源极/漏极区域。铜金属化完成了正面加工。

步骤2:晶圆间键合和晶圆减薄

将包含器件和BPR的晶圆翻转,将“有源”正面键合到毯式载体晶圆上。这一过程在室温下采用SiCN-SiCN电介质熔融键合,然后在250°C下进行键合后退火。然后,将第一片晶圆的背面减薄至SiGe蚀刻停止层的位置。减薄过程通过依次进行背面研磨、化学机械抛光(CMP)以及干湿蚀刻步骤来实现。下一步是去除SiGe层,然后晶圆即可进行nTSV工艺。

步骤 3:nTSV 处理并连接到 BPR

在沉积背面钝化层后,通过硅对准光刻工艺从晶圆背面对nTSV 进行图案化。nTSV 蚀刻穿过硅(深度达数百纳米),并落在 BPR 的尖端。接下来,用氧化物衬垫和金属(钨)填充nTSV。在此具体实现中,它们以 200 纳米间距集成,不会占用标准单元的任何面积。该流程通过处理一层或多层背面金属层来完成,通过 nTSV 将晶圆背面与正面的 BPR 电连接。

免责声明:作者尊重知识产权、部分图片和内容来源于公开网络,版权归原撰写发布机构所有,如涉及侵权,请及时联系删除。

Reference:1.B. Cline et al., ‘Power from below: buried interconnects will help save Moore's Law,’ in IEEE Spectrum, vol. 58, no. 9, pp. 46-51, September 2021, doi: 10.1109/MSPEC.2021.95310122.‘Arm shows backside power delivery as path to further Moore’s Law’, IEEE Spectrum, 20193.A. Veloso et al., ‘Enabling logic with backside connectivity via n-TSVs and its potential as a scaling booster’, 2021 Symposium on VLSI Technology, 2021, pp. 1-2