您当前的位置:检测资讯 > 科研开发

嘉峪检测网 2025-09-03 19:58

在做MCU选型时,很多工程师可能会重点关注芯片的静电指标作为产品设计的重要参考。

那么,问题来了。

如果你要做一款满足产品接触8KV,空气放电15KV的产品,是不是选一颗HBM静电为2KV的芯片就一定比1KV的更好?

为了搞清楚这个问题,我们按以下几点拆解:

1)芯片的静电和产品静电的区别。

2)正常的产品生产工艺,芯片的静电指标要求是多少?

3)从芯片规格书来看芯片静电和产品静电的对应关系。

4)从实际数据来看芯片静电和产品静电的对应关系。

5)为什么芯片HBM指标越高,产品静电并不一定更好?

下面分别说明:

1、芯片的静电和产品静电的区别。

芯片静电:

要了解芯片静电,最直接的办法就是看芯片的规格书上写了啥。

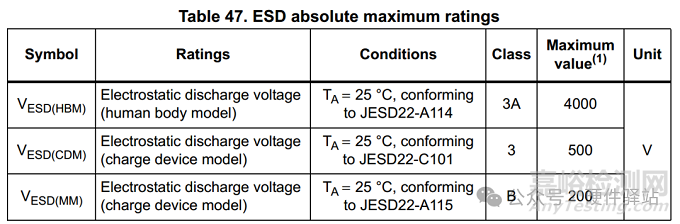

比如,这款STM8AF5268TCY的规格书给出了芯片静电的各项指标,包括HBM,CDM和MM。

需要补充说明的是,MM静电测试现在并不是强制测试要求,因此现在大部分芯片的规格书只能看到HBM和CDM的测试数据。

芯片静电的设计目的是芯片在生产、运输和组装过程中避免因为静电导致损坏,芯片静电测试是在芯片不加电的条件下进行测试的。

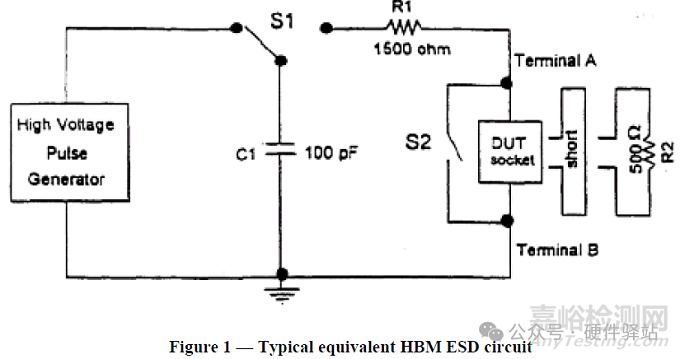

HBM静电(Human Body Model,人体放电模型)是静电放电(ESD)测试中最常用的模型之一,用于模拟人体接触电子器件时因静电积累导致的放电现象。

芯片的HBM测试简图如下,简单理解就是100pF电容通过1.5K电阻对芯片管脚放电。

CDM静电(Charged-Device Model,充电器件模型)是芯片静电放电的另一种模式,用于模拟电子器件在生产、运输或使用过程中因摩擦或感应带电后,通过引脚对地放电的场景。

产品系统级静电:

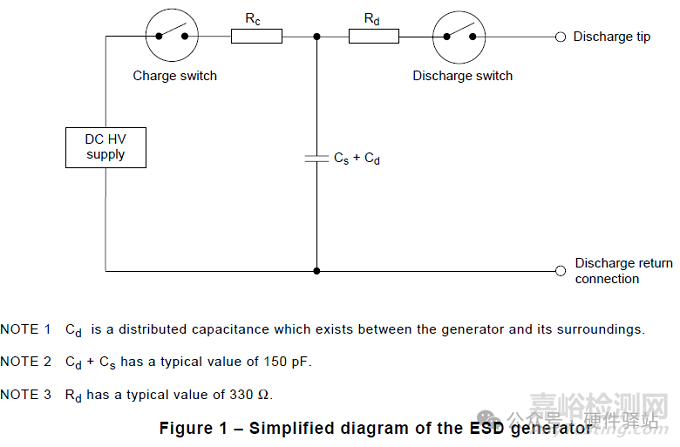

系统级静电(System-Level ESD)是指电子设备在终端使用环境中因人体接触、摩擦或外部电场作用产生的静电放电现象,其防护重点在于整机或系统而非单个芯片,测试标准为IEC61000-4-2,系统级静电又分接触式和空气式两种方法。

系统级静电的测试简图如下,简单理解就是150pF电容通过330欧姆电阻对产品放电。

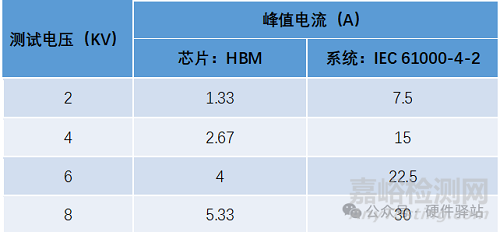

两种标准的放电电阻差异较大,导致放电的峰值电流差异也较大,对比如下表:

简单理解就是同样的静电电压,系统级静电测试更严苛。

2、正常的产品生产工艺,芯片的静电指标要求是多少?

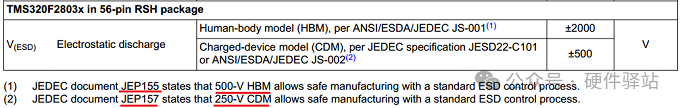

我们再来看TI的一份芯片规格书上面怎样写的。

从上面的信息可以看出,如果在一个静电受控的生产环境,MCU的HBM和CDM指标分别为500V和250V就足够了,至少在生产制造环节,芯片不会被损坏。

我们打开JEP155这篇文档,看看为什么500V的HBM就足够了。

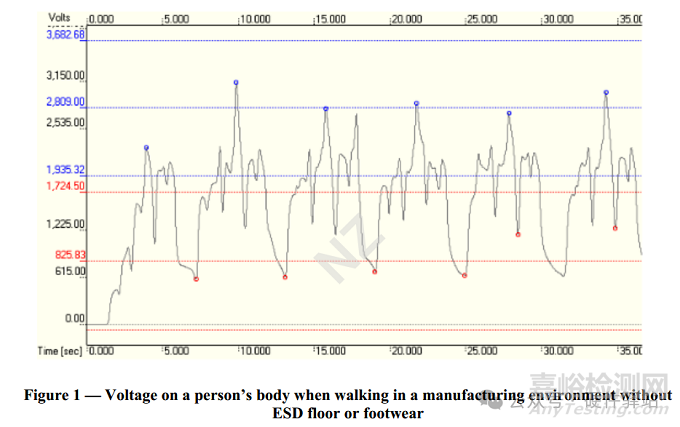

1)假设,刚开始,老板没钱,工厂不愿意做任何ESD防护,一个人在不做ESD处理的制造环境行走,可以产生接近3000V的静电。

按这个环境生产电子产品,一些静电只有2000V或以下的芯片,就难以避免静电损坏。一个可预期的结果就是生产的产品会出现质量问题。这个时候,老板就得做一下整改。

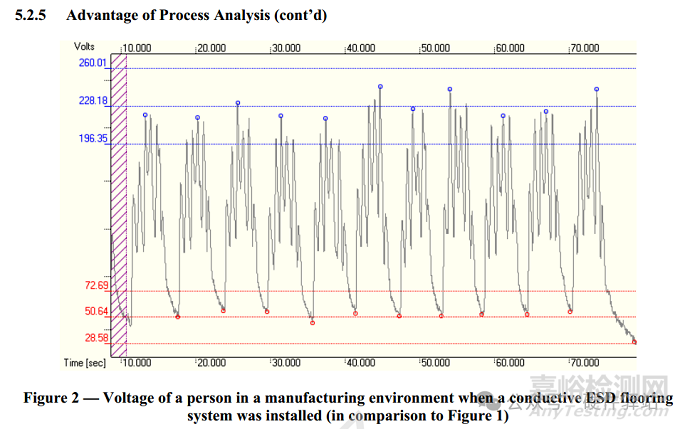

2)先投点小钱,把工厂的地板改造为防静电的,这个时候,员工测试ESD的数值如下:

可以看出,加了钱就是不一样,静电从3000V掉到了260V以下,这个环境对所有芯片静电指标为500V以上的已经足够友好了。

但是,某一天,来了一个客户要求生产组装一款包含有GaAs工艺的放大器芯片产品,此芯片的HBM ESD只有250V,这个时候,老板又考虑了一下,还得加钱。

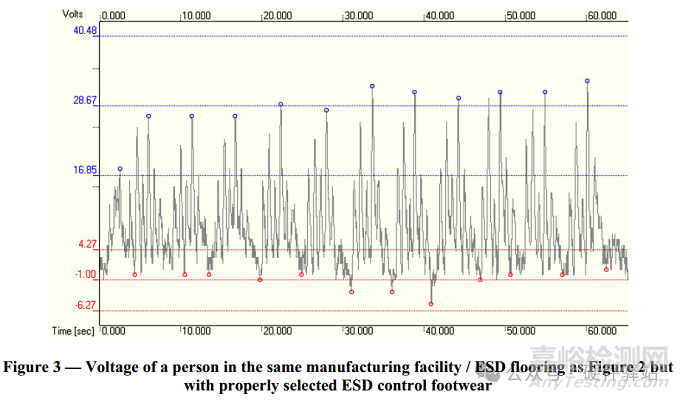

3)于是所有的员工都穿上了防静电鞋,带上防静电手环,员工测试ESD的数值如下:

静电电压从260V掉到了不超过40V,这下老板再也不担心工厂的静电问题了。

以上就是有关芯片HBM指标为什么设计为500V就可以确保生产中不被损坏的详细解释,CDM的相关说明大家可以参考JEP157文档说明,不再赘述。

3、从芯片规格书来看芯片静电和产品静电的对应关系。

我们继续,下面讲一下MCU的HBM静电和系统静电是否有相关性,说得更直白一点就是我选的MCU静电指标越高,是不是做出来的产品静电指标就更好。

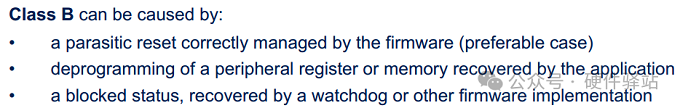

意法半导体的一篇文档AN1709对此进行了相关说明。提出了一项指标叫FESD,就是采用系统级的静电枪测试芯片管脚,标准不再是HBM,而是IEC61000-4-2。

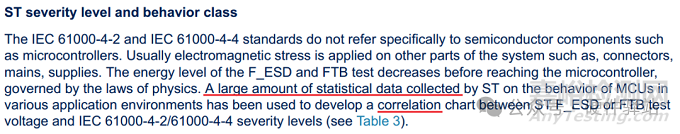

通过大量数据搜集,ST还给出了该指标用于产品上的系统指标对照列表如下:

比如说,用一个IEC61000-4-2的静电枪打芯片,测试芯片1.2KV PASS,1.5KV FAIL,那么这颗MCU在产品上预计能够达到系统级的等级3水平,也就是接触6KV。

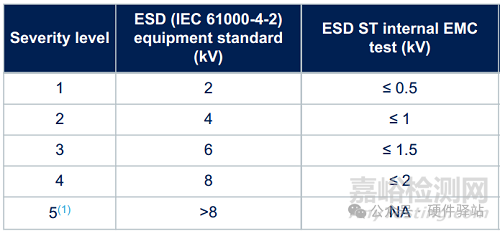

另外需要补充一点的就是,系统级静电的测试标准除了电压等级之外,失效模式分类也更复杂。一共4类。

A类最牛,静电测试时啥影响都没有。

B类也还行,系统打复位或死机(开启了看门狗后可恢复)都算,系统可自行恢复。

C类和D类就没啥意思了,没听说那家客户可接受的。

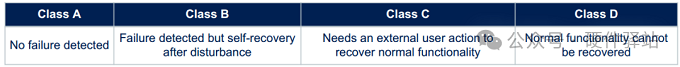

B类的详细解释如下:

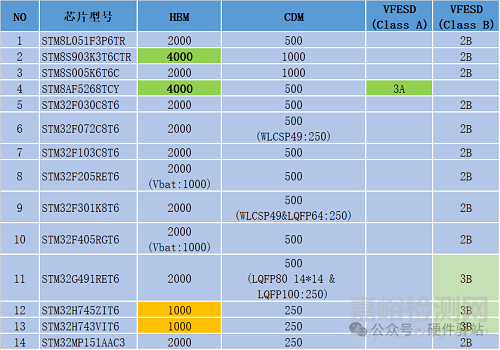

为了分析芯片静电和系统静电是否有关系,随机找了ST的各类型MCU芯片的指标对比如下:

备注:芯片型号是针对某一具体封装,静电指标是手册给出的此系列所有芯片的指标。

可以看出如下信息:

1)VFESD指标大都只给出了等级B的标准数据,A等级的只有一颗芯片数据提供。

2)HBM为4000V的,VFESD有2B和3A两种数据。而两颗HBM为1000V的芯片,VFESD也能达到3B。

3)HBM一列,有两颗芯片的Vbat指标偏弱。

4)CDM一列,有三颗芯片用不同封装,指标会下降。

下面分别说明:

1)芯片A等级,意味着更严格的测试标准,而B等级则相对容易达成一点,比如,如果某产品测试时允许复位,在开发中,可以通过软件的方式做一些处理,在芯片可能导致C类失效前通过软件提前复位芯片,提升B类测试的电压等级。

芯片规格书如果未提供A等级的指标,而你的产品要求是A等级的,那就得实测。

2)从HBM的数据和FESD的数据关系来看,两者并不具备关联性,因此,如果一个芯片设计工程师如果仅仅想依靠提升HBM的数据指标提高芯片在产品上的静电性能并不一定是一种很有效的方法,且会导致芯片成本上升。

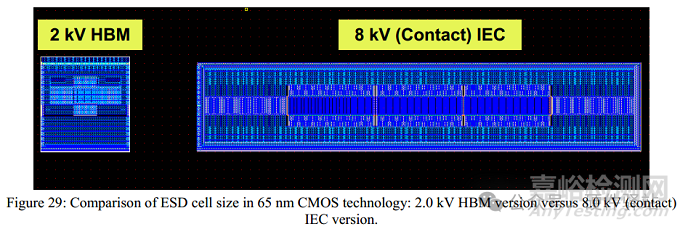

下图是一款芯片从HBM 2KV提升到IEC 8KV的芯片面积对比,供参考。

3)Vbat管脚通常用来外接纽扣电池,需要低功耗设计,推断ESD设计策略和其它管脚可能存在不同的电路方案。

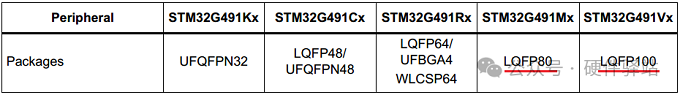

4)CDM测试这一列,有3颗芯片存在CDM的指标和封装具有相关性,我们拿11行的STM32G491这颗芯片看看有没有规律。下划线红线的两种封装CDM值弱于其它封装,那就查找一下大封装的芯片的封装参数。

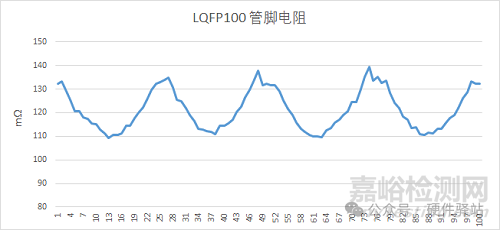

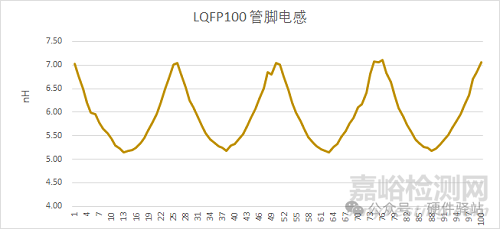

通过IBIS模型提取LQFP100封装的RLC参数如下表,电阻在120毫欧左右,电感在6nH左右,并且出现了4个极值波峰,正好对应芯片的4个边角。

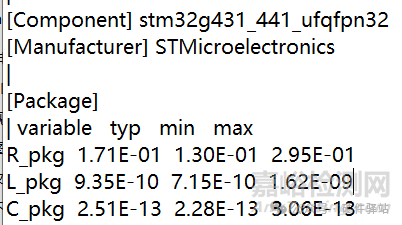

我们再看看最小封装UFQFPN32的参数,这个系列的芯片IBIS模型没有查到数据,G431芯片提供了如下参数,可以作为参考。电感值的范围为0.935nH~1.62nH,比大封装小不少。

以上只是讲了如何通过IBIS模型提取封装RLC参数,至于CDM测试结果和封装有什么关系,读者朋友可以自行研究。

从上面芯片规格书可以看出,芯片的静电指标越高,系统指标不一定更好。

4、从实际数据看芯片静电和产品静电的对应关系。

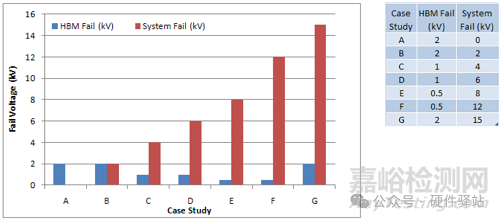

下图为一官方网站给出了7个案例的芯片静电和系统静电对应的关系,可以看出两者没有关联性。

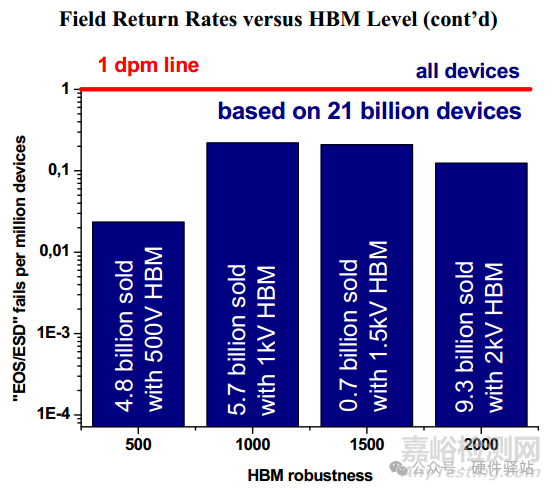

下图为JEP155B文档给出的不同HBM指标的产品返修率,可以看出,并不是HBM最高为2KV的产品返修率最低。

5、为什么芯片HBM指标越高,产品静电并不一定更好。

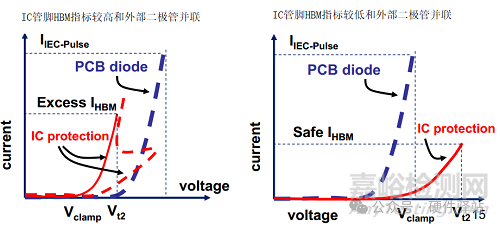

参考下图:

左图为HBM指标较高的芯片管脚和外部静电二极管并联,此片内保护的电路的钳位电压更低,动态电阻更小(二极管上升斜率更陡)。

对比右图可以看出,在芯片片外和片内的联合静电保护设计中,左边的设计更容易把静电引入芯片内部,导致片类保护电路电流过大而超出电流限值,片外的静电二极管的保护作用发挥不出来。

而右图的HBM指标更低的芯片,ESD能量基本都被片外静电二极管所消耗,从而起到了保护芯片的作用。

总结:

芯片的静电指标HBM设计为最低500V,CDM最低250V,就可以满足在受控的静电生产环境不被损坏。

通过多种数据表明,并不是芯片静电越高,产品的抗静电指标就越好;开发者需要评估提升芯片静电指标增加的成本是否合理。

如果系统静电是按A类标准而不是B类标准要求,比如,打静电时不能复位,而芯片静电设计的HBM和CDM指标是体现不了此项设计的预期指标的。当然,系统复位也和芯片的外围电路设计息息相关,仅根据芯片的指标也不能完全决定系统的指标。

来源:硬件驿站