无源器件在电路中一直扮演着很重要的角色,同样在ESD设计中也需要应用无源器件,亦或是无源器件也同样要承受ESD冲击。所以这一期针对无源器件:电阻在ESD设计中的应用与面对ESD的失效机理做一个讨论。

1.1N-diffusion resistor的ESD应用。

N-diffusion resistor在ESD防护电路中主要有如下应用:

CDM防护的串联电阻。

N-well与P-sub的寄生二极管用以CDM防护。

NMOS的镇流电阻

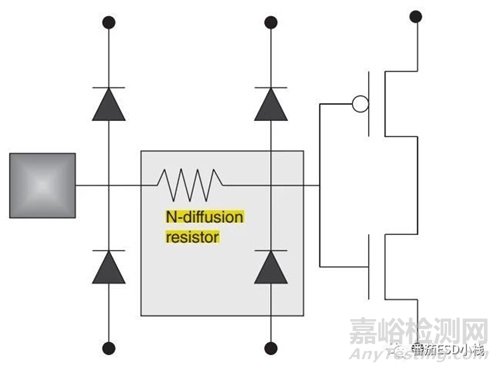

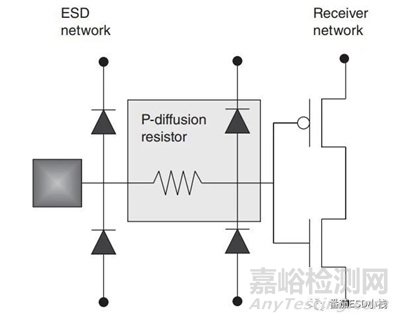

图一.在HBM-CDM二级防护中的N-diffusion电阻。

在该结构是最为常见的针对IO接口的ESD防护电路,该电路中靠近PAD端的二极其设计目的是针对HBM进行防护,所以尺寸很大,导通电阻较小。而后一级的二极管只需要针对CDM进行防护,所以尺寸较小。而两级二极管之中的N-diffusion电阻的作用一便是作为串联电阻,确保HBM的ESD电流不会流入第二级中。因为第二级的尺寸较小,过电流能力弱,所以需要N-diffusion电阻让第二级在HBM中只分流较小的电流。(CDM和HBM的区别前面的文章已经提到过,针对这种超高频的静电流,只需要寄生电容很小的二极管便能实现泄放)

作用二是N-diffusion与P-sub构成了一个寄生二极管。当P-sub中集聚了大量电子且PAD接触到导体后,P-sub中的电子利用该寄生二极管泄放CDM电流,从而实现对NMOS的CDM保护作用,避免Gate损坏。(目前这种设计比较少见)

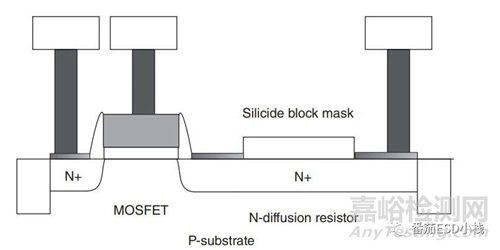

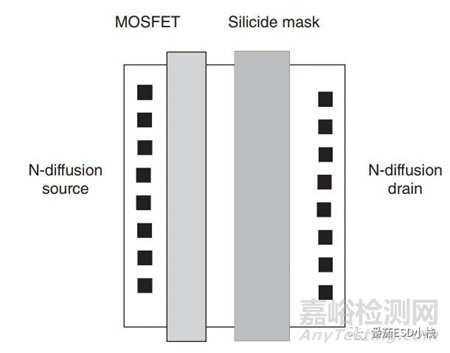

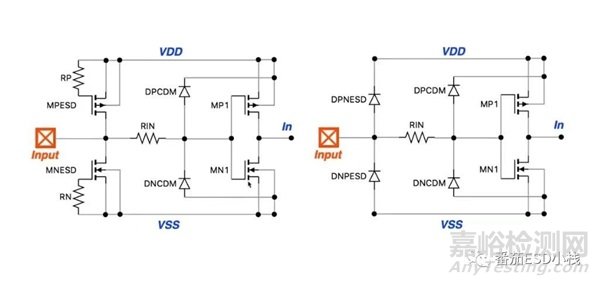

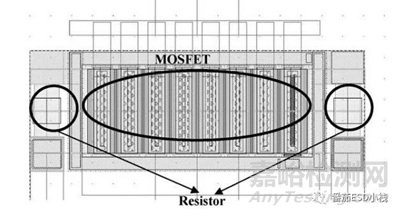

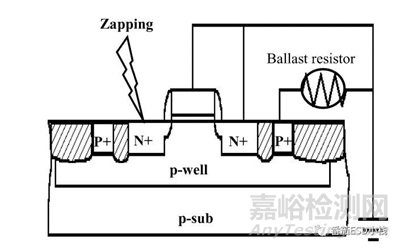

图二. N-diffusion电阻作为NMOS镇流电阻。

图三. N-diffusion电阻作为NMOS镇流电阻。

无论是GGNMOS还是GCNMOS都需要NMOS的drain端直接承受ESD的冲击,所以为了避免MOS管的损坏,需要在drain端设计镇流电阻,一方面能确保ESD电流的均匀分布,一方面能保护器件不在ESD中损坏。除了用N-well resistor 作为NMOS镇流电阻外,还可以将drain端拉宽,并进行salicide block处理。

1.2 N-WeLL resisitor的ESD作用。

N-Well电阻在ESD防护电路中主要起到的是镇流电阻的作用。

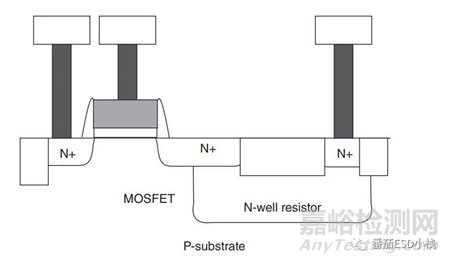

图四.N-well resistor 作为NMOS镇流电阻。

这种设计的目的与N-diffusion电阻作为NMOS镇流电阻的设计思路一致。但是N-Well镇流有其独特的优势:

1.因为N-Well的存在,ESD电流需要流过Nwell才能到达drain端,其镇流效果更好,NMOS的drain端承受的静电作用较少。

2.N-Well中载流子浓度较低,所以这种镇流结构中N-well与MOS中N+接触面会存在异质结,该异质结有利于GGNMOS中寄生三极管的击穿。

3.不需要silicide block的mask。

4.与NMOS的集成度更高,能降低接触电容。

图五.N-well resistor 作为NMOS镇流电阻。

2. P-diffusion resisitor的ESD应用

P-diffusion resisitor的应用与N-diffusion resistor的应用类似,主要作用于HBM-CDM二级防护中,一二级间的分流电阻,避免二级保护被HBM所损坏。同时P-diffusion resisitor中的P+与PMOS中的N-Well形成一个寄生二极管,实现对N-WeLL中积聚的负电荷的泄放,实现对PMOS的CDM防护。另外P-diffusion resisitor也可以实现对GDPMOS中PMOS源端的保护。

图六.在HBM-CDM二级防护中的P-diffusion电阻。

3. POLY 电阻的ESD应用

1.1与2.1已经提到了diffusion电阻用于CDM防护,但是这两种电阻有个明显弊端,N-diffusion只能保护NMOS,P-diffusion只能保护PMOS,但是PMOS和NMOS都有CDM损坏风险,diffusion电阻无法做到两者兼顾。目前最主流的HBM-CDM二级防护的结构如图所示:

图七.POLY电阻的ESD应用。

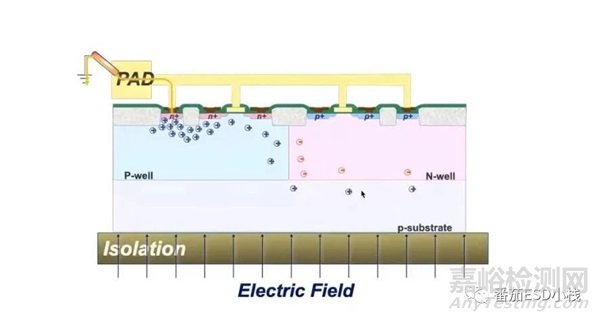

用POLY电阻作为二级防护的电阻,让其只起到分流的作用。把P-diode与PMOS做到同一个阱中,当PMOS中的N-WeLL中因为外界电场积聚了很多负电荷后,负电荷可以通过P-diode与N-Well间的寄生二极管泄放到PAD,实现对PMOS的CDM防护。同理把N-diode与NMOS做到同一个阱中,当在外界作用下NMOS中的P-Well积聚了大量正电荷,这些正电荷便可通过N-diode泄放,实现对NMOS的CDM防护。

图八.N-diode实现NMOS的CDM防护机理示意图。

POLY电阻用于二级防护,需要根据前后级的类型选择阻值,如果前后级都是二极管,其阻值不需很大。如果前后级是GGNMOS等需要击穿的器件,阻值就需要大一些。

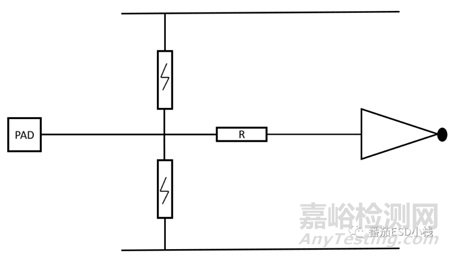

有些设计会在ESD防护单元后加电阻,如图所示。

图九.ESD后置POLY电阻。

该电阻的作用是保护Input buffer的栅极。ESD器件的Second break down Voltage 的电压会分压一部分到电阻上,从而保护了内部电路的栅极。

POLY电阻还应用于体镇流电阻,用来提高器件的ESD鲁棒性。

图十.体镇流电阻版图。

体镇流电阻的作用是通过镇流电阻,促使体电位分布均匀,使得GGNMOS等器件在应对ESD电流时均匀开启,提高ESD过电流能力。同时,该电阻能减少GGNMOS进入Holding Voltage后的开启电阻。

图十一.体镇流电阻示意图。

4.电阻的ESD失效分析

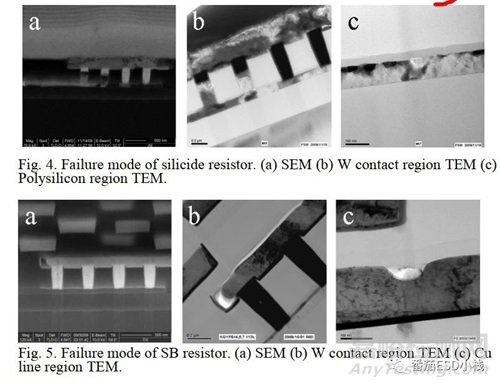

在电路中无论是ESD防护单元还是其他单元,都有承受ESD冲击的风险。这里讨论下电阻在ESD下的失效机理。电阻在面对ESD时的失效原因是由不同材料接触面的热失配梯度造成(不同材料的接触面产生热力学梯度,时间一久或者梯度过大,就会造成失效)。目前主流工艺结点下,接触孔主要是由钨做成,互联主要由Cu组成。Silicide电阻和Silicide Block电阻的失效位置和机理有所区别。Silicide电阻的失效主要发生在接触孔和poly的接触面,因为钨合金和poly上的NiSi缓冲层的方块电阻差值较大,当过大的电流通过时,poly接触面与W接触孔产生热梯度,从而造成失效。Silicide Block电阻主要失效点在Cu互联,因为Silicide Block电阻的电阻率更大,POLY和NiSi缓冲层的结温度更高,而Cu互联更易受高结温的影响,该高温会传递到Cu互联上从而造成失效。

图十二.两种电阻失效后的SEM/TEM图片。

可以看出Silicide电阻的失效主要发生在钨合金的接触孔和多晶硅处。而Silicide Block电阻的失效主要发生在Cu互联上。

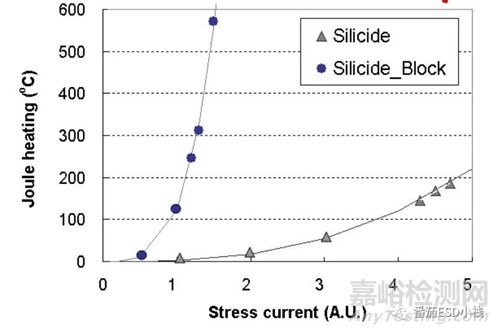

图十三.两种电阻电热特性对比。

从图中可以看出两种电阻电热特性差距较大。Silicide Block电阻阻值较大,但是节温上升幅度大,ESD下容易失效。而Silicide电阻阻值较小,但是结温度上升较慢,针对ESD的鲁棒性较好。

之前我手头一个项目就是IO接口处的电阻发生了失效,当时出于面积的考虑选用了类似Silicide Block的High POLY电阻,所观察的现象也是连接金属出现问题。而出现该问题是因为ESD模块与内部器件不匹配,通过调整ESD模块解决的这个问题。