1、背景介绍

在汽车电子的许多应用中,负载需要通过一条较长的输出线连接到主板上。如图1所示,典型应用有Class-D,LED,USB充电器等。往往此时的传导EMI会更加严重,这次分享就是针对这一问题来分析和进行改善。

图 1:汽车电子中需要长线负载的应用

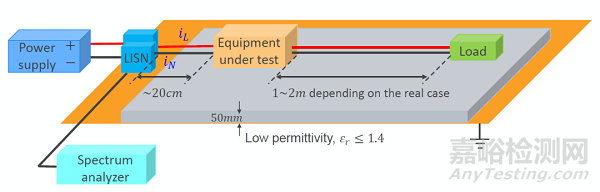

首先我们来看一下测试装置

在测试这些负载的传导EMI时,输出线的长度应该保持和实际应用一致。因此,基于汽车电子CISPR-25测试标准,测试装置如图2所示:被测设备(EUT)距参考地(铜板)5厘米,之间为低介电常数介质(相对介电常数小于1.4);输出线为1~2米,取决于实际应用情况;LISN接在电源和EUT之间,为噪声回路提供恒定的阻抗(对共模来说,这个阻抗为25Ω)。

图 2:汽车电子长线负载测试装置

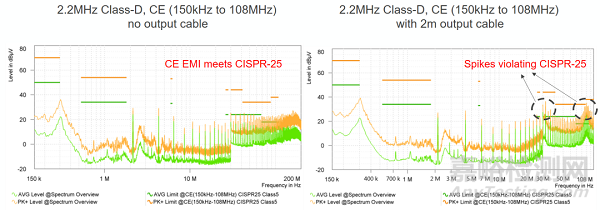

图3对比了MPS的同一个车载Class-D功放(2.2MHz,BTL,24.5W,模拟输入Class-D功放)在加输出线和不加输出线的传导EMI测试结果。从图中可以看出,在没有输出线的情况下,它的EMI可以满足CISPR25的要求,但是,在有2m输出线的情况下,EMI明显变差,尤其是在30MHz和90MHz左右出现两个峰,导致EMI难以达标。

图 3:汽车电子长线与无输出线负载传导EMI对比

针对这一问题,我们将先介绍长线负载的共模EMI模型,并由此解释了测试中的现象,并介绍了降噪方法。

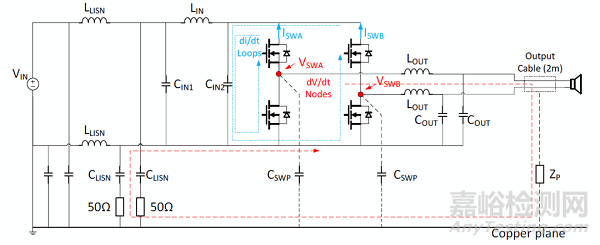

那么下面让我们以一个Class-D功放为例,先来看一下传导的共模EMI模型。

2、长线负载EMI模型

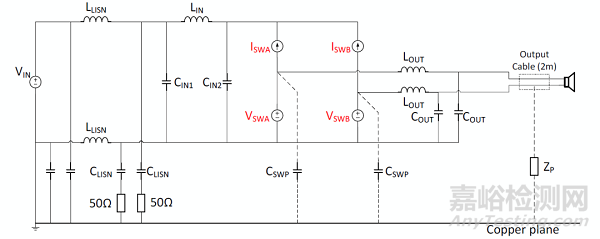

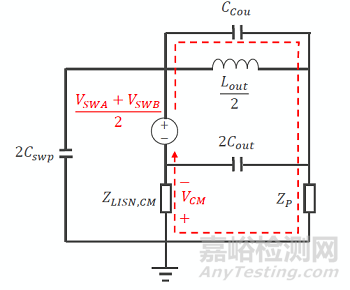

图4展示了Class-D的拓扑及其传导共模噪声路径。共模噪声由电路中开关频率的dv/dt节点和di/dt环路产生,通过输出滤波器到输出侧,再通过输出侧对地的阻抗到参考地上,最后从LISN流回EUT。由此也可以看出,输出线对地的寄生阻抗(ZP)在分析传导EMI上很重要。除此之外,CSWP为dv/dt节点对参考地的寄生电容,也为共模噪声提供了一条通路。

图 4:Class-D功放的共模噪声路径

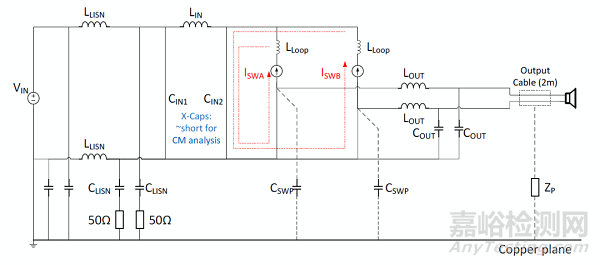

根据我们熟悉的替代定理(Substitution Theorem),在分析EMI问题时,我们可以用电压源或者电流源对开关上的电压或者电流进行等效替代。图5为应用了替代原理之后的电路图。

图 5:应用替代定理分析Class-D功放的共模噪声

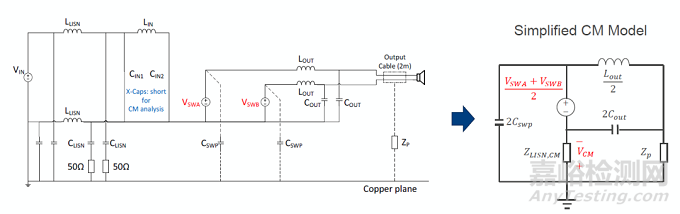

下一步,每个噪声源产生的噪声可以用叠加定理来进行分析,图6和图7分别表示电流源以及电压源的分析,可见,在这个模型中,电流源并不会独自产生噪声,但电压源可以,我们也可以依此得到图7中初步的共模模型。

图 6:应用叠加定理分析Class-D功放的共模噪声电流源

图 7:应用叠加定理分析Class-D功放的共模噪声电压源

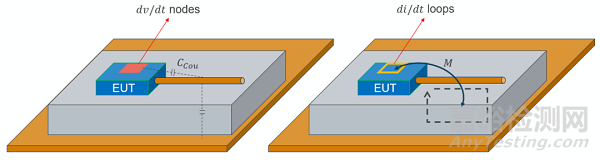

值得一提的是,到现在我们还没有考虑近场耦合的问题。然而,在实际中,因为输出线是一个很大的导体,它和EUT之间的近场耦合往往是不能忽略的。近场耦合分为电场耦合和磁场耦合两种,下面我们将逐一讨论。

电场耦合指的是,电路中某一导体(如开关节点SWA,SWB)和另一导体(如输出线)之间有寄生电容,若该导体为高频dv/dt节点,那么会有噪声电流流向另一导体,从而产生EMI噪声,如下图左图所示。而磁场耦合指的是,电路中某个环路(如开关与输入电容之间的环路)和另一环路(如输出线和参考地之间的环路)有互感,如果该环路为高频di/dt环路,则会在另一环路上产生感应电动势,从而产生EMI噪声,如下图右图所示。

图 8:电场耦合与磁场耦合

若考虑电场耦合,图7中的模型可以用图9加以修正,其中CCou代表从开关节点耦合到输出线上的电容,可见,在高频时,这个电容阻抗很小,会将噪声电流旁路,并造成EMI问题。

图 9:考虑电场耦合的EMI模型

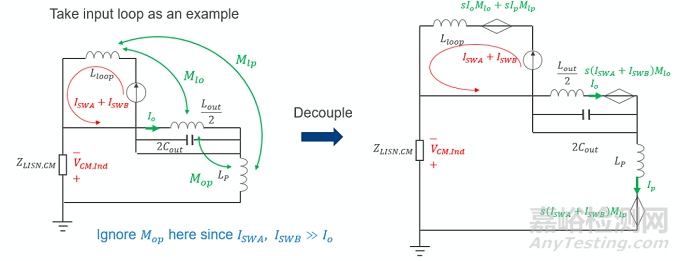

另一方面,若考虑磁场耦合,我们会发现,图6中的di/dt环路是可以产生磁场耦合的,模型可以用图10加以描述,在解耦之后,我们发现共模路径中多了一个噪声源,其大小与di/dt的强度,以及输入环路和输出线对地环路之间的互感成正比。

图 10:考虑磁场耦合的EMI模型

在以上的讨论之后,让我们来揭开最后一部分阻抗,即传输线对地阻抗的神秘面纱。

3、输出长线对地阻抗的分析

因为输出线很长,在传导的高频频段,我们需要考虑它的传输线效应。电力电子工程师朋友们在日常工作中可能很少会用到这部分的内容,因此首先介绍一下相关的概念。

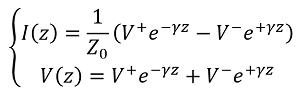

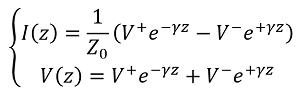

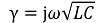

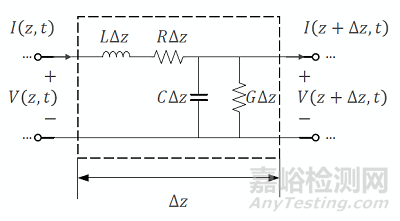

当电路尺寸与要考察的频率对应的波长相近时,电路的相关参数,如电压、电流、阻抗等,会由集中参数变为分布参数。对于传输线的每一小段,如图11(a)所示,我们可以考察它的单位电感、电阻、电容以及电导。最终,传输线上电流以及电压的分布可以用式(1)表示:

(1)

(1)

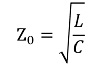

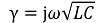

其中,Z0为传输线特征阻抗,γ为传输常数。当传输线上的损耗(R与G)可以忽略时,Z0和γ可以用(2)和(3)表示:

(2)

(2)

(3)

(3)

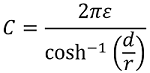

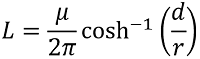

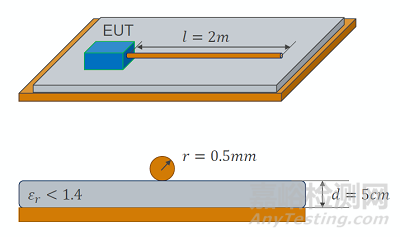

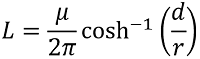

由于我们的输出线有如图11(b)所示的几何形状,这些参数都可以通过电磁场理论求出。当不考虑损耗时,我们主要关心单位电感与电容,它们分别由式(4)和(5)表示。其中,d表示线与参考地的距离,r表示线的半径,ε为介质的介电常数,µ为介质的磁导率。这里因为是共模噪声,所以输出的两条线近似合并为同一导体考虑。

(a)

(b)

图 11:(a)传输线模型;(b)输出线对地的几何模型

(4)

(4)

(5)

(5)

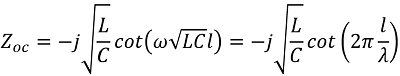

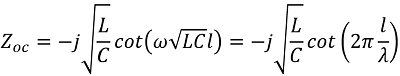

最后,由于我们的输出线的末端与参考地之间没有连接,可以认为是近似开路(末端电流为0),我们可以将(2)-(5)代入到(1),得到最终输出线上的电流与电压表达式。因此,可以得到,对于长度为l的输出线,它的阻抗ZOC可以用(6)表示:

(6)

(6)

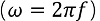

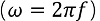

其中ω为角频率  ;

;

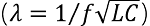

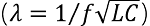

而λ即为波长  。

。

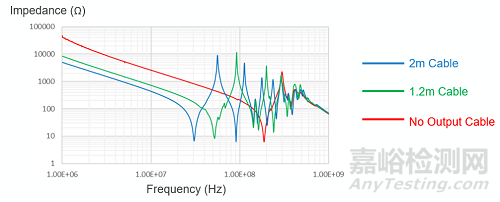

通过(6),根据三角函数的性质,在l为四分之一波长的奇数倍时(如1/4λ,3/4λ等),这个阻抗将发生串联谐振,导致EMI传播路径上的阻抗大幅减小,因此,我们会发现有EMI峰的存在。如果传输线长为2m,那么根据我们的实际情况,1/4λ,3/4λ对应的频率分别在31.6MHz和95.1MHz,这也就解释了为什么图3的频谱上会出现这两个峰。

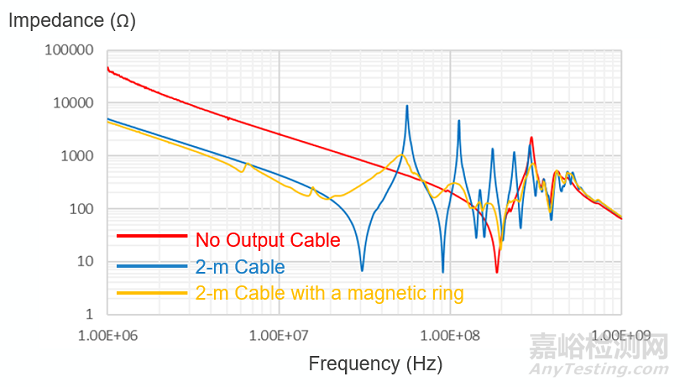

图 12:不同长度传输线的对地阻抗测量结果

这个理论也很容易直接通过测量进行验证。图12为不同长度传输线的对地阻抗测量结果,显然,对于2m的输出线,其阻抗谢振峰的位置符合我们之前的计算结果,这也解释了EMI测量结果中的谐振峰。另外,输出线越短,谐振发生的频率也越高。

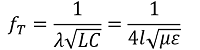

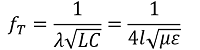

最后,我们可以将1/4λ对应的频率表示为(7):

(7)

(7)

从(7)可以看出,输出线与参考地的距离,以及线径,都不会影响这个谐振的位置,谐振只与输出线的长度有关。

由此,我们得到了完整的传导共模EMI模型,下面我们就来看一下有什么方式来降低噪声。

4、降噪措施与实际应用

基于噪声的模型,我们列出了一些通用的降噪方法:

减小高频噪声源,如降低开关波形的斜率;

通过抖频等方式降低高频噪声;

在布线时,尽可能减小dv/dt节点以及di/dt环路的面积;

在回路上加共模滤波器,或者在输出线上加磁环;

有条件的话,可改变输出线长避开敏感频段;

加屏蔽罩以解决近场耦合问题。

其中,后三点是针对输出长线负载的降噪手段,我们分别来看一下效果。

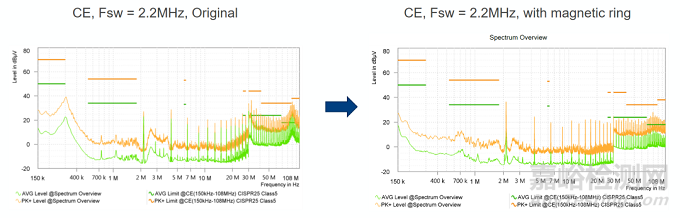

首先,是在输出侧加磁环(加在靠近板子的一端),图13对比了加与不加磁环时的输出线对地阻抗,可见,在加磁环之后,对地阻抗明显增大,可以避免谐振的影响。图14则比较了输出线有无磁环时的传导EMI。可见,磁环有效地抑制了高频的谐振峰。

图 13:输出线加磁环后的对地阻抗

图 14:输出线有无磁环时的传导EMI测试结果

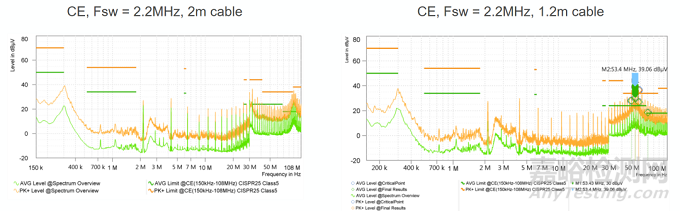

其次,是通过改变线长来改变谐振峰的位置,如图12所示,当线长为1.2m时,3/4λ对应的谐振峰在108MHz以上,已经避开了FM波段(76MHz - 108MHz)。因此,当测试允许改变线长的时候,这也不失为一种降噪手段。图15比较了线长为2m和1.2m时的传导EMI结果。显然,后者的谐振仅有位于53MHz左右的一个峰。

图 15:输出线长为2m和1.2m时的传导EMI测试结果

最后,基于第二节的介绍,我们可以通过消除输出线与测试板之间的近场耦合来降低EMI。屏蔽罩的材质可以为金属,要包裹电路中的dv/dt节点与di/dt环路,且屏蔽罩需要接地(接到靠近噪声源的地)。

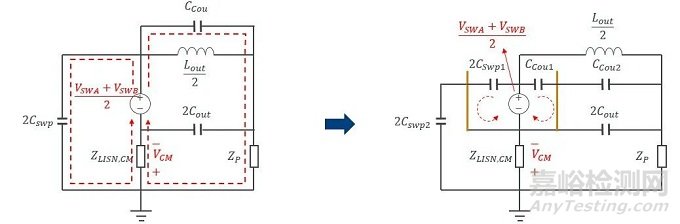

图16说明了接地对于电场耦合的效果。当dv/dt节点被屏蔽后,原来直接对参考地对输出线的杂散电容Cswp和CCou变成了其对屏蔽罩的杂散电容Cswp1和CCou1。当屏蔽罩接地的时候,噪声电流直接流回噪声源的地,不会经过LISN,因此也就没有共模噪声了。(如果不接地的话,由于屏蔽罩对于参考地以及输出线仍有杂散电容,噪声电流仍然会流到参考地上,无法起到降低EMI的效果。)

图 16:接地屏蔽罩对于电场耦合的影响

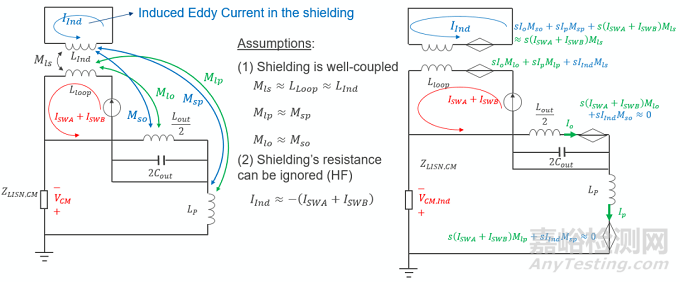

图17说明了接地对于高频磁场耦合的效果。当di/dt节点被屏蔽后,在理想情况下(屏蔽罩与di/dt环路的耦合非常好,高频时屏蔽罩的阻抗基本为感性),屏蔽罩可以产生一个涡流抵消原来di/dt环路对外界的影响。解耦后,如图17右侧所示,原来磁场耦合产生的感应电压源可以被屏蔽罩抵消。

图 17:屏蔽罩对于高频磁场耦合的影响

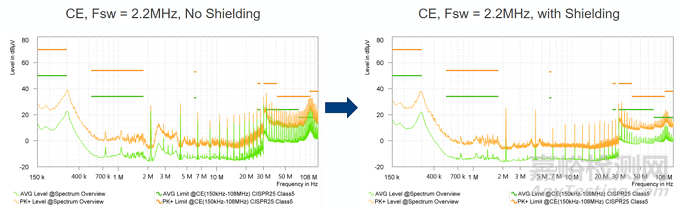

从EMI测试结果也可以验证,在加上屏蔽罩之后,如图18所示,传导噪声有明显的改善,在有2m输出线的情况下也可以满足CISPR25-Class5的要求,并有6dB的裕量。

图 18:有无接地屏蔽罩的传导EMI测试结果对比

另外,在这次分享中,我们虽然是以一个Class-D功放作为例子,但是,文中提到的方法也适用于其他的芯片哦。比如MPS公司产品 --- MPQ7200,它是一个同步LED驱动,它使用了抖频,对称VIN设计等一系列手段降低EMI(具体技术可以参考我们去年的EMI话题分享)。

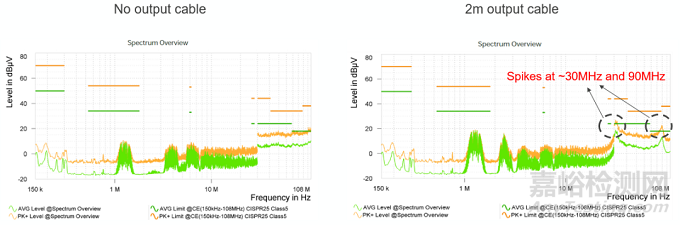

如图19所示,当没有输出线时,传导EMI噪音非常低,但当加上2m输出线时,它也会在对应的位置出现两个谐振峰。

图 19:MPQ7200有无2m输出线时的传导EMI测试结果

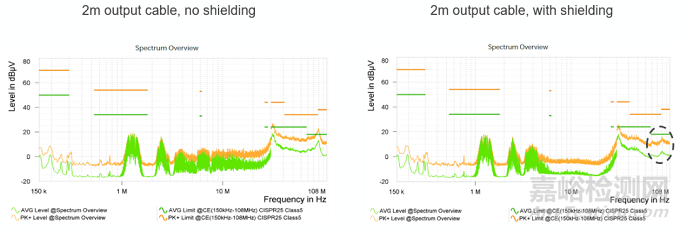

同理,通过加屏蔽罩的方式,如图20所示,我们可以减少它的传导噪声,这一效果在高频尤其明显。这也说明了这次分享中提到的原理和降噪措施对于各种变换器拓扑都是通用的。

图 20:MPQ7200有无屏蔽罩时的传导EMI测试结果。

最后,我们来进行一下总结,在本次分享中,我们先介绍了高频共模传导EMI的建模,并在模型中考虑了电场耦合和磁场耦合的影响;之后,我们通过传输线理论解释了输出带长线负载的传导EMI结果为什么会出现谐振峰,并可以准确预测它的位置;最后,我们介绍了一系列的通用的EMI降噪方法并进行了对比。

(1)

(1) (2)

(2) (3)

(3)

(4)

(4) (5)

(5) (6)

(6) ;

; 。

。

(7)

(7)