您当前的位置:检测资讯 > 检测案例

嘉峪检测网 2025-09-09 12:01

一前言

随着电子设备向高集成度、高速率方向发展,电磁兼容性(EMC)问题日益突出。其中,时钟信号作为数字系统的核心,其高频特性极易引发电磁干扰(EMI)。晶振作为关键时钟源,其设计不当往往导致辐射超标,成为EMC测试中的常见问题。本文将结合实际案例,探讨晶振时钟的EMI抑制方法。

二晶振时钟的EMI问题分析

时钟信号因其周期性特点,在频域表现为离散的窄带噪声,能量集中,易导致辐射(RE)测试超标。晶振布局不良时,高频谐波会通过PCB走线或引脚辐射,成为主要干扰源。

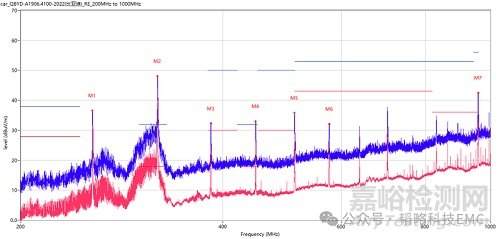

图1 机器时钟超标数据

【晶振引发EMI的两大主因】:

1.高频谐波辐射

晶振输出的方波信号含丰富奇次谐波(如8MHz晶振的3次谐波24MHz、5次谐波40MHz等),这些高频成分通过走线或寄生参数形成辐射。

2.PCB布局缺陷

晶振引脚走线过长、阻抗失配、悬空引脚未接地,或靠近敏感信号线,均会加剧串扰和辐射。

三晶振引脚接地的EMI抑制机制

图2 无源晶振

对于无源晶振(图2),将晶振的空置引脚接地可显著改善EMI性能,这一措施通过优化电路的高频特性,从多个维度抑制电磁干扰,具体作用如下:

1.屏蔽效应

接地引脚为晶振金属壳体提供低阻抗路径,减少高频噪声通过寄生电容耦合至周边电路。

2.优化回流路径

缩短高频噪声的返回路径,降低环路面积,抑制共模辐射。

3.稳定参考电位

避免浮空引脚因电磁场耦合引入外部噪声或成为辐射天线,接地后不仅能消除电场干扰,还能减少潜在的磁场耦合路径。

四案例分析:8MHz晶振辐射整改

1.问题现象

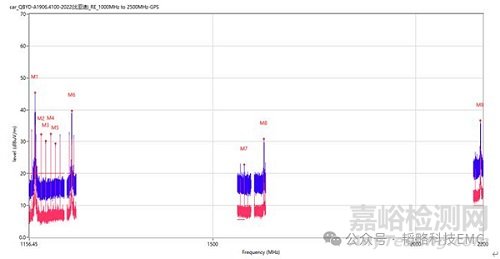

在机器设备RE测试中,8MHz晶振的高次谐波(1160MHz、1168MHz等),可从下面测试数据得知,在喇叭天线测试频段出现时钟倍频辐射超标(见图3)。

图3 整改前的RE测试数据

2.整改措施

【问题定位】:

频谱分析确认超标频点为8MHz倍频,排查发现无源4脚贴片晶振两接地引脚处于悬空状态。如下图4所见。

图4 PCB Layout图

【优化方案】:将悬空引脚进行接地处理(见图5),确保低阻抗回流路径。

图5 整改措施图片

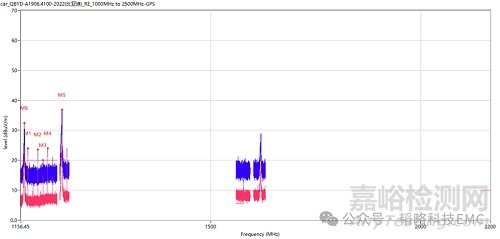

3.整改效果

接地后,辐射噪声降低10dB以上,测试数据显著改善(见图6)。

图6 整改后的RE测试数据

五 总结与建议

1.关键设计原则

晶振布局优先:缩短走线、匹配阻抗、远离敏感电路。

悬空引脚接地:避免浮空引脚因电磁场耦合引入外部噪声或成为辐射天线。

2.EMC优化方向

源头抑制:选择展频IC或展频晶振,优化时钟驱动电路。

路径阻断:完善屏蔽设计,确保低阻抗接地。

⚠注:本文基于工程实践经验,具体设计需结合实际测试验证。

来源:韬略科技EMC