您当前的位置:检测资讯 > 科研开发

嘉峪检测网 2025-08-02 21:45

一、为什么需要2.5D及3D封装?

摩尔定律精准预言了近几十年集成电路的发展。然而,逐渐逼近的物理极限、更高的性能需求和不再经济的工艺制程,已引发整个半导体行业重新考虑集成工艺方法和系统缩放策略,意味着集成电路产业已经步入后摩尔时代。

超越摩尔通过三维堆叠来实现多个芯片在平面和垂直方向的互连,用系统集成的策略来大幅度提升空间利用率。垂直互连技术从纵向维度进一步扩展,促进了系统级集成的不断进步。转接板形式的通孔技术是最有前景的互连方案之一,已成为全球先进封装的研究热点。

二、2.5D及3D封装的结构组成

2.5D/3D先进封装技术是芯片系统关于延续摩尔定律的有效解决方案之一,该技术主要目的是通过在垂直方向上堆叠芯片以实现更高密度的集成。

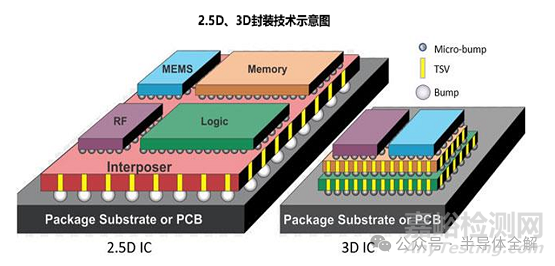

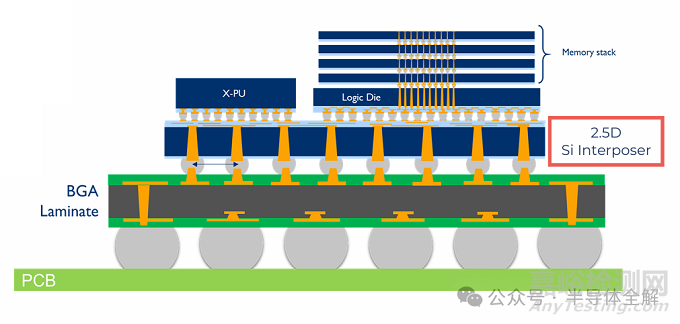

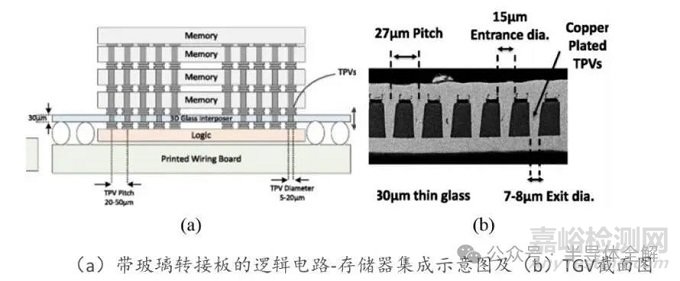

其中,3D封装技术与2.5D封装技术的差别主要在于3D封装技术是通过硅通孔(ThroughSiliconVia, TSV)或玻璃通孔(ThroughGlassVia, TGV)把所有芯片都垂直连接,而2.5D封装技术指的是将多个芯片平铺在中介层上,中介层上有再布线层,用于芯片间的水平互连,而中介层再通过通孔把芯片与封装基板相连,进而实现多个芯片的垂直互连,这种将多种不同材质、尺寸、功能封装到一个系统内的技术也被称作三维异质集成技术,其中实现中介层互连功能的关键工艺则是相应的通孔制备及孔金属化。

三、转接板(中介层)的典型结构

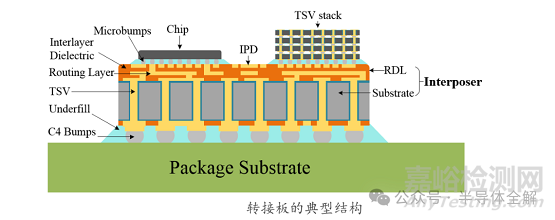

转接板(中介层)主要包括基底和RDL。其上层RDL通过微凸块与搭载的有源芯片相连,这些有源芯片可以是普通的二维芯片,也可以是三维的芯片堆叠。其下层RDL(或者是焊盘)通过普通的凸块或者焊球与封装基底相连,实现转接板与封装管壳的电气连接。转接板的典型结构如图所示。

转接板基板可以是硅、玻璃或者有机高分子材料,上面有贯穿基板的通孔,实现转接板正面和背面的电气连接。转接板上的TSV采用导电材料填充,外侧包覆有绝缘层,对TSV和基底进行隔离。

TSV填充的导电材料通常是铜,也可以是钨、多晶硅等。填充的方式有完全填充和不完全填充两种。

转接板的RDL包括金属布线和绝缘介质层,用来实现搭载的芯片与芯片之间、芯片与TSV之间的互连。金属布线通常是通过电镀铜来制备,而介质层可以是无机介质如SiO2、Si3N4 等,也可以是有机聚合物如聚酰亚胺(PI,Polyimide)、苯并环丁烯(Benzocyclobutene,BCB)等。

在RDL层中,除了互连线以外,也可集成一些无源器件,包括电容、电感、电阻等。这些集成无源器件(IPD,Integrated Passive Device)可组成多种功能电路,起到如去耦合、滤波、抑制开关噪声等作用。

将IPD集成到转接板中,不仅可以减小总体电路的体积,提升系统的集成度,也可以使转接板的功能更丰富,适用面更广。

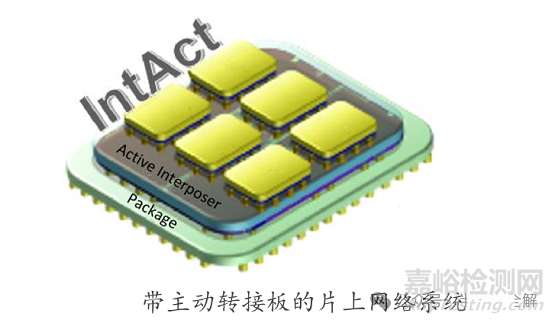

目前绝大多数转接板是无源的,即上面集成的只有布线和无源器件,也有少数研究机构在转接板上制备了CMOS晶体管来实现一些简单功能,这种转接板被称为有源转接板(active interposer)。

比如法国的半导体研究机构Leti在16年提出了一种2.5D封装的片上网络系统(NoC,Network on Chip),在有源硅转接板上排布了6个通信芯片形成通信网络系统,如图所示。转接板本身也制备了CMOS结构,集成了一些简单的功能,包括功率变换和测试电路等。

有源转接板的好处在于,可以将承载芯片的一些简单功能转移到转接板上,或者在转接板上配合相对应的承载芯片增加一些新的功能,这样,不仅可以充分利用转接板上的空间,提高集成度,还能增加系统功能或者提升系统性能。有源转接板的局限在于,在转接板上制备CMOS结构,相当于制备有源TSV芯片,工艺流程比无源转接板复杂的多,成本也高;其集成结构类似3D TSV 封装,也会面临着 3D TSV 封装类似的问题。

四、转接板的分类

按照转接板基底材料的不同,转接板可分为硅转接板(silicon interposer)、 玻璃转接板(glass interposer)和有机转接板(organic interposer)。

1、硅转接板

硅转接板是当前最主流、最成熟的转接板技术,研究的最多,应用也最广泛。硅转接板的迅速发展主要得益于成熟的硅加工工艺和布线工艺,使得硅转接板可与集成电路工艺完美兼容。

硅转接板上TSV孔径可做到10 μm以下,深宽比达到20以上,而RDL线宽可以达到 1μm 以下。另外,硅转接板还具有热导率高、与搭载的芯片CTE匹配等优点。

硅转接板的最大不足之处在于其制作成本昂贵,目前只在少数高端产品中实现量产。目前,硅转接板也面临着一些工艺上的难题,比如TSV的绝缘、薄晶圆持拿等。另外,由于硅并非绝缘体,且介电常数较大(11.2),作为基底时会造成较大的损耗,尤其在高频环境下会导致电路传输特性的下降。

2、玻璃转接板

玻璃转接板和硅转接板结构类似,通过玻璃通孔(TGV,Through Glass Via)实现上下面的垂直互连。

玻璃转接板的优势主要有以下两点:

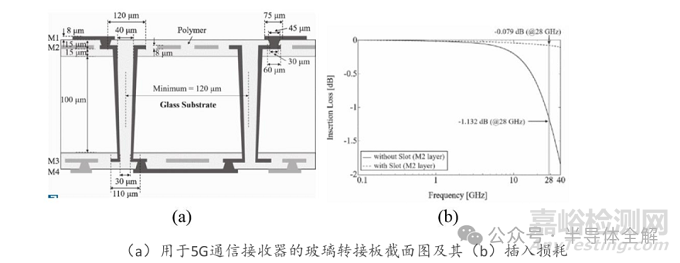

1)玻璃转接板的电学性能表现优异,绝缘性好,具有较低的介电常数(5.3)及损耗角正切值(0.006);

2)玻璃转接板不需要制备绝缘隔离层,使得制备工艺大大简化,具有较低的成本。

此外,玻璃转接板与裸片也有较好的CTE匹配,且不会存在像TSV漏电这样的绝缘缺陷。

而制约玻璃转接板发展的主要因素是玻璃加工及相关配套工艺的不成熟。

例如,TGV打孔工艺,目前只能通过激光刻蚀、喷砂、微机械加工等实现,存在加工效率低、精度低等缺点,孔径通常在几十微米以上,深宽比在10以下。同时,在玻璃上进行细密布线比较困难,无法达到硅转接板的集成密度。

另外,由于玻璃比较脆,会导致加工的良率降低。除了加工工艺不成熟外,散热问题对于热导率低的玻璃转接板来说也是不小的挑战。相对于硅转接板和有机转接板,玻璃转接板最具潜在优势的应用是在高频领域。

韩国科学技术院的Sumin Choi等人对硅转接板、玻璃转接板和有机转接板的信号传输特性进行了对比分析,仿真结果表明,在10GHz的应用频率下,玻璃转接板具有最好的传输特性。

对于高带宽、高传输速率的系统来说,玻璃转接板是三种转接板当中的最佳选择(如果其布线密度能满足需求)。随着高频应用尤其是5G通信的兴起,玻璃转接板在射频领域越来越受业内人士的青睐。

3、有机转接板

有机转接板的最大优势在于其成本低。

有机转接板以有机高分子材料加增强相材料作为中间芯层(core),使用图形化叠加工艺制作金属布线,使用电镀过孔(PTH,Plated Through Hole)实现上下的垂直互连。

这套工艺与倒装焊封装基底制备工艺类似,目前比较成熟,批量制造的成本也很低。

有机转接板的缺点也非常明显,首先,有机高分子材料热膨胀系数比较大,有机转接板与组件的CTE失配比较严重,容易引起热应力可靠性问题,比如转接板的翘曲、介质材料断裂等。

其次,有机转接板的热导率很低,不利于高密度集成的散热。最后,受限于有机转接板加工工艺的精度,其线宽和PTH的大小都无法与硅转接板相媲美,严重阻碍了有机转接板在高集成度、高I/O方面的应用。

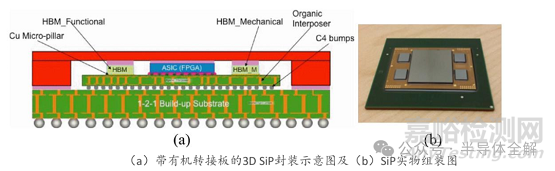

在集成密度要求不高和散热问题不严重时,有机转接板是硅转接板的低成本替代方案之一。 2016年,Cisco公司的Li Li等人提出了一种用于高性能交换机的3D SiP 封装,这是有机转接板的典型应用案例之一。

受光刻工艺的制约,目前主流半导体制造公司生产的硅转接板的尺寸都限制26 mm×32 mm 以内。为了突破该尺寸限制并降低制造成本,Cisco公司选择了有机转接作为SiP集成方案。如图所示,有机转接板的尺寸为 38 mm×30 mm×0.4 mm,其上集成了一个ASIC芯片和4个高带宽存储器(HBM,High Bandwidth Memory)。线宽为6μm,PTH直径为57μm,高度为200μm。频域仿真分析表明,在20 GHz以下时,该SiP集成具有良好的性能,满足使用的需求。作为有机转接板,也有其局限性。由于布线密度不够,为了实现互连的要求,该有机转接板的布线层多达10层,大大增加了转接板的厚度,造成了可靠性隐患。另外,该有机转接板的翘曲高达100μm左右。

五、转接板的应用

为了降低转接板集成的成本,提高转接板性能,很多企业和研究机构对此进行了大量的研究。 在降低制造成本方面,早在1992年,IBM公司就提出了一种转接板的制造方法,先在基板两侧布线,然后在基板上打通孔,在通孔内溅射一层导电金属,再通过丝网印刷的方法,将一种含有金和银微颗粒的热塑性导电聚合物填充通孔。

这种聚合物导电胶不仅用来填充通孔,还起着类似焊球的作用,用来连接上下多层转接板或者芯片,该方法用低成本、耗时短的聚合物导电胶填充来代替高成本、耗时长的TSV铜电镀,可以降低转接板成本,缩短转接板开发周期,但这种方法存在通孔填充不完全的问题,通孔中的孔隙会导致可靠性方面的隐患。

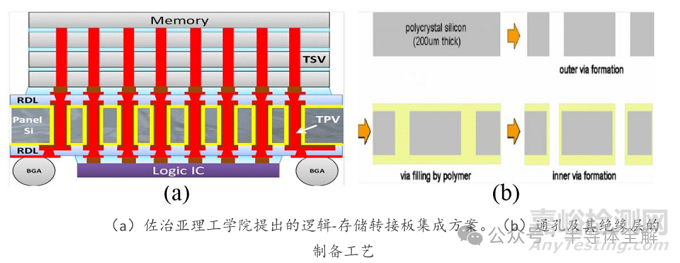

2012年,佐治亚理工学院3D封装研究中心的Sundaram等人提出了一种低成本、低电损耗的转接板,用于逻辑-存储芯片的集成,如下图所示。

该转接板采用多晶硅为基底,制备工艺如下:先使用激光在基底上烧蚀通孔,再使用热压工艺在通孔内填充聚合物,在通孔的聚合物内再打出孔,使用化学镀或者电镀来填充铜,最后再在双面制备RDL。

由于转接板上层及孔内覆盖有厚的聚合物,比起采用薄SiO2做绝缘的常规转接板来说,损耗要低很多。

该转接板的低成本主要来自三方面,一是低成本材料及工艺的运用。大面积多晶硅薄片的成本大大低于单晶硅。多晶硅上用激光烧蚀的方法即可获得小孔径的通孔,比起单晶硅用深反应离子刻蚀(DRIE,Deep Reactive Ion Etching)要简单快捷。

二是工艺步骤的简化。采用薄晶圆打通孔再涂覆聚合物绝缘层的方法,避免了转接板的背面减薄和背面制备绝缘层的工艺。

三是便于批量化生产。超大面积的多晶硅面板使得每个面板上的转接板数量大大增加,降低了单个转接板的成本。

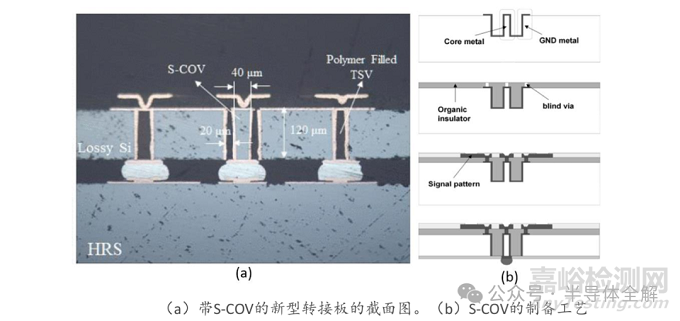

2017年,韩国电子技术研究院的Lee等人提出了一种低成本、低TSV插入损耗的新型TSV转接板,应用于高频RF器件当中。该转接板使用了特殊的硅核心同轴通孔(S-COV,Silicon-Core Coaxial Via)替代传统TSV,其结构如图(a)所示,通孔内部有一个硅轴心,硅轴心外层和孔侧壁层都包覆着一层金属铜,分别作为信号通道和接地通道,在孔侧壁与硅轴心之间填充有机聚合物,其制备工艺如图(b)所示。

得益于厚的有机聚合物隔离层以及信号-接地的同轴结构,这种通孔的插入损耗要优于传统 TSV。而且,该通孔不需要进行完全铜填充的电镀,只需要有铜导电层,节省了电镀时间和成本。

硅转接板集成技术兼容性好、可靠性高、设计灵活性强,是目前先进封装技术中比较切实可行的方案之一,在工业界内得到了大量的应用。

这些应用中既有同质芯片集成以扩充芯片容量/运算能力,也有异质芯片集成以形成SiP。

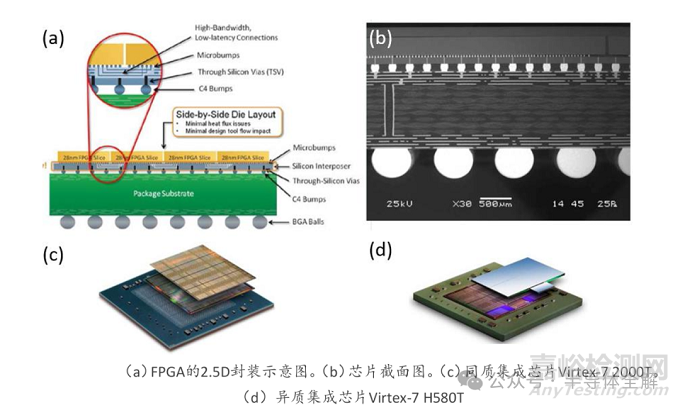

在硅转接板的发展历程中,第一个引人瞩目的商业产品当属Xilinx公司2011年公布的FPGA芯片Virtex-7 2000T,如图所示。

该FPGA芯片采用台积电的CoWoS(Chip-on-Wafer-on-Substrate)28nm工艺,将4个FPGA裸片(die)排布在25 mm×31 mm大小的硅转接板上,使得单片FPGA上逻辑单元的数量达到了200万个,是非三维集成单片FPGA容量的2.8倍。2012年,Xilinx公司又推出了一款FPGA产品Virtex-7 H580T,在硅转接板上集成了2个FPGA裸片和一个收发器裸片,实现了转接板上异质芯片的集成。

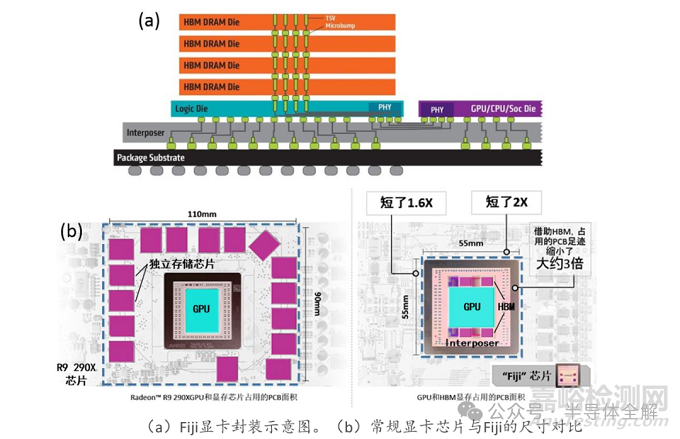

高端显卡也是硅转接板应用的一个主要领域。为了增强显卡的性能、降低功耗,AMD公司于2015年发布了一款采用硅转接板集成的显卡Radeon R9 Fury X(Fiji),将显卡核心(GPU/CPU/SoC)与显存以及逻辑芯片集成在一个封装中,如图所示。

比起上一代非三维封装显卡Radeon R9 290X,该三维封装显卡的带宽增加了60%,每瓦性能提高了两倍多,芯片大小也缩减到原来的1/3以下。之后,ADM和NVIDIA公司又相继推出了多款基于硅转接板封装的显卡产品,比如NVIDIA于2016年推出的Tesla P100及AMD于2017年推出的Radeon Vega。这两款显卡产品比起Fiji来说,线宽更小,集成度更高,性能也有了进一步的提升。

六 、硅转接板技术面临的挑战

尽管硅转接板技术拥有诸多优势,拥有非常好的应用前景,但目前仍面临着一些产业和技术方面的挑战,制约着硅转接板技术的应用和进一步发展。

(1)最主要的制约因素是工艺成本高。

首先,转接板制造包括TSV电镀、多余铜去除、减薄、临时键合/解键合等一系列工艺,流程复杂,不仅工艺成本高,流片周期也长。

其次,由于整个工艺步骤多,且不完全成熟,因此良率不高,这也导致硅转接板的制造成本进一步增加。

(2)硅转接板制备工艺本身还不成熟,面临一些技术方面的挑战。

比如,转接板的光刻(包括大尺寸的限制、TSV背面对准以及翘曲对光刻精度的影响等)、晶圆减薄和持拿、TSV无孔隙电镀等关键工艺还有待改进。

另外,TSV漏电流、转接板翘曲以及热应力等问题也有待进一步解决。

(3)TSV堆叠的方式突破了传统芯片的二维结构,而与之相适应的设计软件及测试方法还很缺乏。

(4)产业环境还不完全成熟。

目前芯片设计、制造和封测各自分离的格局不利于转接板集成技术的发展,还需要产业链的整合。此外,业内对转接板技术也未统一标准。

好了,这篇关于先进封装转接板的知识就到这儿,欢迎关注《半导体全解》,后续将会介绍更多半导体的知识!

参考文献:

(1)罗江波 高性能硅转接板的系统设计及集成制造方法研究[D].

(2)吴道伟 高密度2.5D_TSV转接板关键技术研究[D].

(3)©Yole Intelligence 2024 High End Performance Packaging 2024

www.yolegroup.com[C].

(4)闵球 三维封装集成电路中的电热特性分析研究[D].

(5)龙致远 电子互连微孔金属化方法及机理研究[D].

来源:半导体全解