您当前的位置:检测资讯 > 行业研究

嘉峪检测网 2025-07-23 22:51

一、TSV 三维封装技术的发展及现状

随着半导体产业的发展,电子器件的体积逐步减小,功能日益强大,成本也越来越低,极大地促进了电子产品在日常生活和生产中的广泛应用。

反过来,电子器件的广泛应用,如物联网、智能终端、工业智能化的兴起,又对电子器件的高密度集成、多功能化和低功耗提出了更进一步的要求。

在摩尔定律时代,芯片尺寸的缩小是通过缩小线宽来实现的。而近年来,芯片线宽的缩小似乎已经进入了一个瓶颈,芯片在平面上的尺寸缩小变得非常困难。实现多功能集成的片上系统(SoC,System on Chip)也面临着尺寸扩大、互连太长而导致的诸多问题。

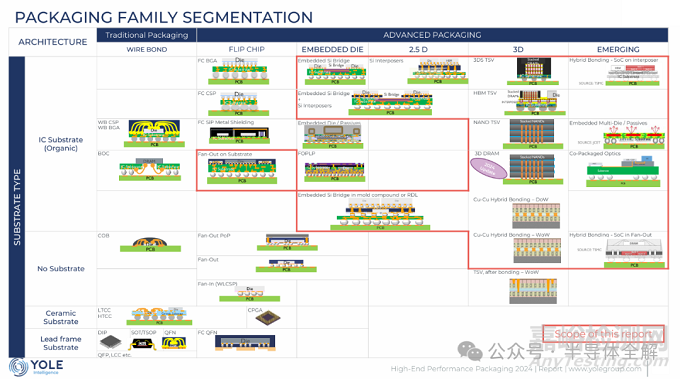

为了进一步满足多功能化和高密度集成的要求,突破芯片尺寸的瓶颈,业内开始从封装方面寻求解决的办法,各种先进封装技术也因此应运而生,包括系统性封装(SiP,System in Package)、扇出型晶圆级封装(FOWLP,Fan-Out Wafer Level Packaging)、晶圆级封装(WLCSP ,Wafer Level Chip Scale Packaging)、扇出型封装(InFO,Integrated Fan-Out)以及硅通孔(TSV,Through Silicon Via)三维封装技术等,如图所示。

这些先进封装技术的运用,可使芯片能够在不改变原有线宽的基础上,进一步减小体积、缩短互连、提升性能以及降低功耗。

TSV 三维封装是通过 TSV 实现垂直方向多芯片互连的一种封装技术,具有互连线短、集成密度高、功耗低等优点,是最有望实现“超越摩尔”(More than Moore)战略的封装解决方案,也是先进封装领域的研究热点之一。

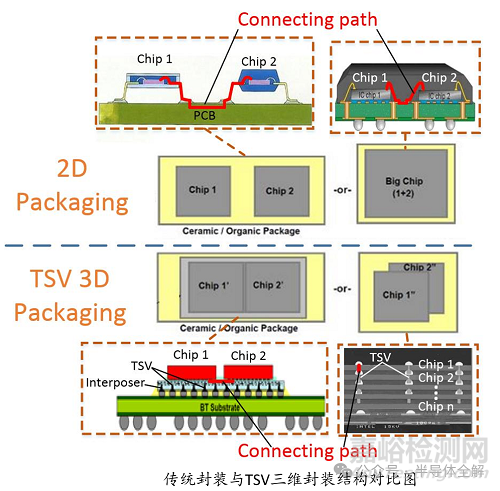

如图所示,在传统的二维封装中,裸片与裸片之间的连接路径要经过打线键合、导线架甚至PCB布线等,距离很长,而在TSV三维封装中,裸片之间的连接只要通过上下层的TSV或转接板上的再布线层(RDL,Redistribution Layer)就能实现。

TSV三维封装突破了平面集成的限制,显著的缩短了互连长度,进而降低了互连线上损失的功耗,降低了信号的RC延时,能大幅提高芯片的集成度和性能。

虽然TSV技术近年来才成为研究的热点,但是硅通孔概念的雏形在1956年就已经出现。晶体管的发明者之一William Shockley在专利中提到了在晶圆上制作深通孔(deep pits)用以使信号从晶圆的一面传输到另一面。

“Through silicon via” 这个术语则由Sergey Savastiouk在文章中最先提出。第一次将TSV技术用于量产商业化产品当中的是惠普公司,其在1976年发布的单片微波集成电路(MMIC)产品中首次使用了贯穿IC芯片的通孔技术来实现接地,但这款产品中的TSV并不是用来实现三维封装。业界普遍认为,第一个量产的TSV三维封装产品是东芝公司2008年生产的图像传感器,该传感器使用了芯片上的通孔将传感芯片上的信号引出到背面的基板。

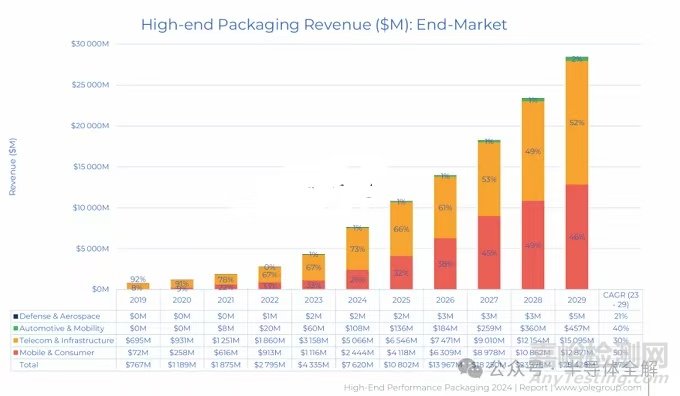

TSV三维封装的应用也越来越广泛,其应用领域包括微机电系统(MEMS,Microelectromechanical Systems)、CMOS图像传感器(CIS,CMOS Image Sensor)、现场可编程逻辑阵列(FPGA,Field Programmable Gate Array)、高带宽内存(HBM,High Bandwith Memery)等,如图所示。

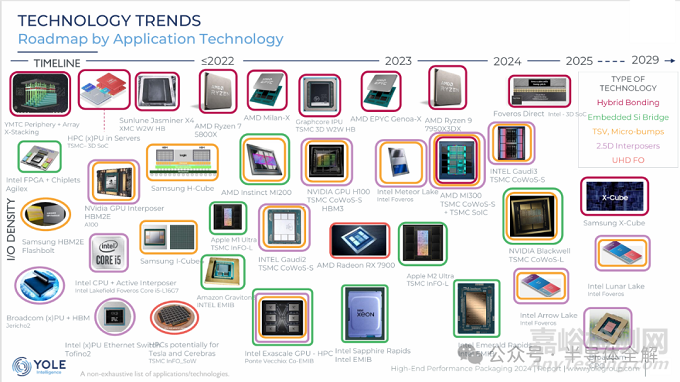

下图是YOLE预测在接下来几年,先进封装在不同行业应用增长情况:

二、TSV三维封装技术的分类及优缺点

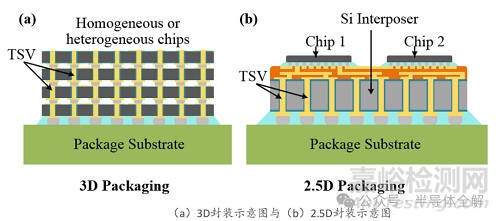

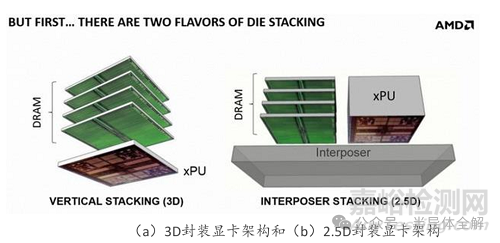

TSV三维封装技术通常分为两类,一类是3D封装,即通过微凸块(microbump)和硅通孔连接上下层芯片,将多颗有源芯片在垂直方向上堆叠,如图(a)所示。

3D封装集成的可以是同质芯片,比如多个快速闪存芯片的堆叠,也可以是异质芯片,比如逻辑芯片、存储芯片、RF芯片等集成一体形成系统。

另一类是2.5D封装,即在无源的转接板上排列多种同质或异质芯片,通过RDL和微凸块实现各芯片间的电气连接,并通过转接板上的TSV将电源/信号引入转接板背面,与封装基板相连,如图(b)所示。

TSV 3D封装和2.5D封装有各自的优势和缺点,适合于不同的制备工艺和应用领域。

3D封装通过TSV垂直连接多层芯片,可以实现芯片之间的最短连接。显然,在目前的先进封装技术当中,它具有最高的集成密度、最小的体积、最低的功耗、最小的RC延时,为芯片设计者和制造商所青睐。

但是,3D封装目前面临的问题同样很突出。

(1)散热问题

3D封装集成密度高,封装中多个有源芯片紧密堆叠,热量集中,非常不利于散热,容易导致芯片结温过高。

(2)热机械可靠性问题

堆叠的各芯片之间由于热膨胀系数不同、温度不同会产生应力,连接芯片之间的微凸块上会形成高应力点,容易产生失效。另外,TSV本身也会产生应力,影响周围晶体管的性能。

(3)良率问题

3D封装工艺复杂,很多技术还不完全成熟,如晶圆减薄、薄晶圆持拿、TSV电镀等,因此,相对于传统封装来说,制造良率不高。

(4)设计软件开发

与3D结构相应的电子设计自动化(EDA,Electronics Design Automation)软件还未普及,目前绝大多数EDA软件都只适用于二维结构。

(5)相关产业链还不成熟

例如,缺乏成熟的测试方法和设备,需要已知合格芯片(KGD,Know Good Die)供应商的整合等。

2.5D封装采用带TSV的无源转接板来承载有源芯片,虽然在减小互连长度、提高集成密度方面略逊于3D封装,但其独特的优势使得2.5D封装能缓解上述问题,成为目前最切实可行的三维封装方案。

与3D封装相比,其优势包括:

(1)能缓解芯片内部的热应力

首先,搭载的有源芯片中并不需要有TSV,硅转接板中虽然有TSV,但是没有晶体管,不存在TSV应力对晶体管影响的问题。其次,转接板在有源芯片和封装基底之间,能缓解有源芯片与封装基底之间的热失配,减小热应力。

(2)降低热量累积

2.5D封装的结构避免了有源芯片的堆叠,减小了热流密度,且无源的硅转接板可以增加热量在芯片内水平方向的传导,增强芯片的散热,降低芯片热集中点的温度。

(3)设计和集成的方式更灵活

3D封装中,堆叠的芯片通常要求采用统一的设计标准和工艺标准(包括线宽、节距等),避免堆叠的不匹配,而2.5D封装中,可以将不同功能、不同生产商生产的不同标准的芯片集成在一起。

(4)与现有IC工艺及封装工艺兼容性好

2.5D封装中,承载的有源芯片可以是现有的普通芯片,不需打TSV孔,也不需另行设计。管壳的封装也可使用现有的倒装焊技术。在布线设计时,可将芯片及转接板RDL布线当做二维平面来看待,使用现有的EDA软件。

(5)封装方案可移植性好

3D封装方案需要根据不同的应用,对有源芯片进行重新设计,而一套成熟的2.5D转接板集成封装技术可很容易的移植到不同的应用上,只要将转接板的 RDL布线重新做设计,不需要对搭载的有源芯片做改动,可大大节省开发的时间和成本。

三、先进封装的应用

2.5D转接板集成和3D封装各有优势和劣势,选择哪种集成方式需要根据相应工艺、搭载芯片类型等具体考虑。

例如,AMD公司在选择新一代的三维封装显卡架构时,可能的选择有完全的3D堆叠,将显存直接堆叠在显卡核心芯片XPU(GPU或CPU)上,如图(a);或者2.5D封装,通过硅转接板将XPU与显存集成,如图(b)。

显然,前一种方案能实现互联更短,面积更小,但是最终AMD选择的是硅转接板集成方案。这样选择的可能是出于降低风险的目的。首先,要在XPU上堆叠显存,就必须在其上制作 TSV孔,这样需要对XPU的架构及工艺进行重新设计,加大了开发的风险和成本。其次,显存和XPU的功耗都不低,且其本身的28纳米工艺也存在着发热量巨大的问题,因此3D堆叠可能会导致非常严重的热问题,影响器件的可靠性和性能。而2.5D封装不需要对现有芯片进行改变,可直接使用现成的KGD,保证良率。

同时,硅转接板对热源进行了分散,缓解了各部件的热失配问题。另外,在硅转接板上,XPU和显存的连接路径虽比3D堆叠长一些,但是比起独立封装或者打线键合来说还是有了巨大的改进。因此,硅转接板2.5D封装是一种比较稳妥的解决方案。

下图是关于封装的发展展望,可以预见接下来的几年,先进封装技术将得到质的飞跃,且封装形式也会越来越多样。

后续的文章将介绍更多先进封装的细节,这篇关于先进封装简单的介绍就就到这儿,欢迎关注《半导体全解》,后续将会介绍更多半导体的知识!

参考文献:

(1)罗江波 高性能硅转接板的系统设计及集成制造方法研究[D].

(2)吴道伟 高密度2.5D_TSV转接板关键技术研究[D].

(3)©Yole Intelligence 2024 High End Performance Packaging 2024

www.yolegroup.com[C].

(4)闵球 三维封装集成电路中的电热特性分析研究[D].

(5)龙致远 电子互连微孔金属化方法及机理研究[D].

来源:半导体全解