您当前的位置:检测资讯 > 科研开发

嘉峪检测网 2019-02-15 10:06

本文主要介绍可靠性试验之ESD的相关模型及测试标准、测试结果及判定、ESD相关防护等。

1、ESD模型

ESD放电模型分下列四类:

人体放电模式(Human-Body Model,HBM)

机器放电模式(Machine Model,MM)

组件充电模式(Charged-Device Model,CDM)

电场感应模式(Field-Induced Model,FIM)

测试模型分为以下两类:

对于系统级产品测试的IEC电子枪放电模式

对于研究设计用的TLP模型

1.1、芯片级测试模型

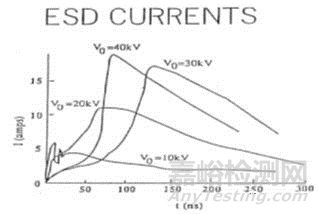

人体放电模式(HBM)的ESD是指因人体在地上走动磨擦或其它因素在人体上已累积了静电,当此人去碰触到IC时,人体上的静电便会经由IC的引脚而进入IC内,再经由IC放电到地去。此放电的过程会在短到几百毫微秒(ns)的时间内产生数安培的瞬间放电电流,此电流会把IC内的组件给烧毁。对一般商用IC的2-kV ESD放电电压而言,其瞬间放电电流的尖峰值大约是1.33安培。

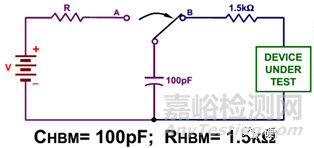

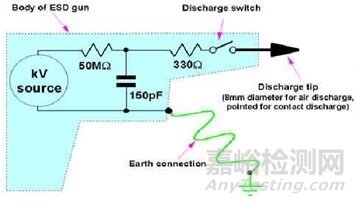

HBM测试模型如下图所示:

不同HBM静电电压与其产生的瞬间放电电流及持续时间的关系如下图所示:

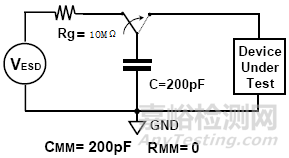

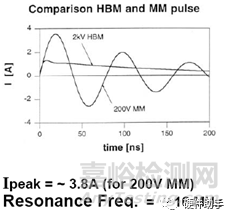

机器放电模式(MM)的ESD是指机器(例如机械手臂)本身累积了静电,当此机器去碰触到IC时,该静电便经由IC的pin放电。因为机器是金属,其等效电阻为0Ω,其等效电容为200pF。由于机器放电模式的等效电阻为0,故其放电的过程更短,在几毫微秒到几十毫微秒(ns)之内会有数安培的瞬间放电电流产生。

MM测试模型如下图所示:

不同MM静电电压与其产生的瞬间放电电流及持续时间的关系如下图所示:

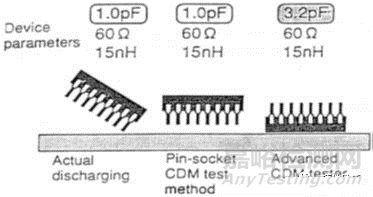

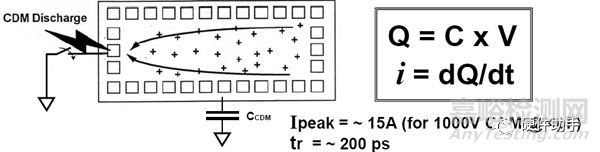

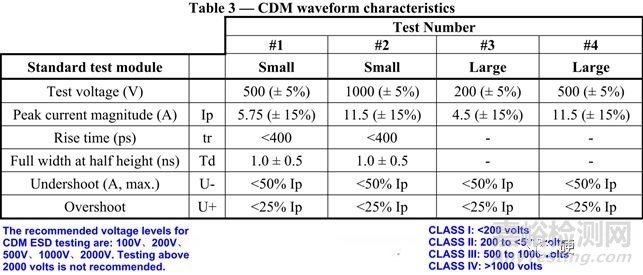

组件充电模式(CDM)是指IC先因磨擦或其它因素而在IC内部累积了静电,但在静电累积的过程中IC并未被损伤。此带有静电的IC在处理过程中,当其pin去碰触到接地面时,IC内部的静电便会经由pin自IC内部流出来,而造成了放电的现象。此种模式的放电时间更短,仅约几毫微秒之内,而且放电现象更难以真实的被模拟。IC内部累积的静电会因IC组件本身对地的等效电容而变,IC摆放角度与位置以及IC所用包装型式都会造成不同的等效电容。此电容值会导致不同的静电电量累积于IC内部。

CDM测试模型如下图所示:

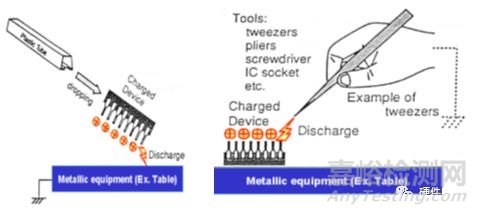

CDM模式ESD可能发生的情形如下:

IC自IC管中滑出后,带电的IC脚接触到地面而形成放电现象。

IC自IC管中滑出后,IC脚朝上,但经由接地的金属工具而放电。

FIM模式的静电放电发生是因电场感应而起的。当IC因输送带或其它因素而经过一电场时,其相对极性的电荷可能会自一些IC脚而排放掉,等IC通过电场之后,IC本身便累积了静电荷,此静电荷会以类似CDM的模式放电出来。

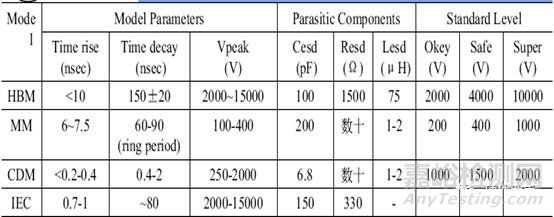

HBM,MM与CDM模型参数比较

1.2、系统级测试模型

系统级测试一般采用静电枪模拟,静电枪模型如下图所示:

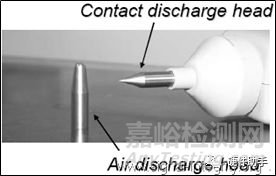

静电枪一般有两种放电头(球头不太常见),如下图所示:

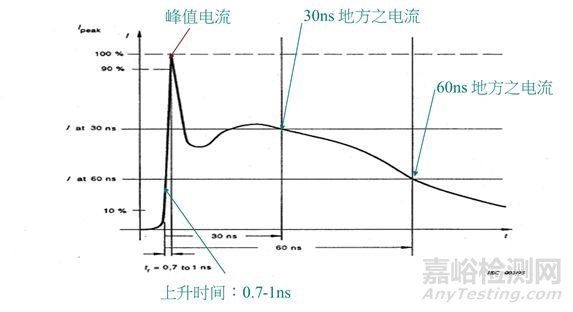

静电放电产生器输出电流波形及参数如下图所示:

不同测试等级的具体电流波形参数不一样,具体见下表:

|

测试等级 |

电压(KV) |

放电峰值电流±10%(A) |

放电开关操作时的上升时间tr(ns) |

在30ns时的电流±30%(A) |

在60ns时的电流±30%(A) |

|

1 |

2 |

7.5 |

0.7~1 |

4 |

2 |

|

2 |

4 |

15 |

0.7~1 |

8 |

4 |

|

3 |

6 |

22.5 |

0.7~1 |

12 |

6 |

|

4 |

8 |

30 |

0.7~1 |

16 |

8 |

2、标准

ESD测试有系统级的IEC61000-4-2测试标准(静电枪模拟放电)和零件级(芯片级)的JEDEC的JESD22-A114(HBM)、A115(MM)、C101(CDM、FIM)测试标准。

IEC61340系列标准:

IEC61340-1:ESD总论

IEC61340-2-1:静电测量方法——带电特性

IEC61340-2-2:静电测量方法——电阻和电阻率

IEC61340-3-1:静电影响模拟方法——静电放电模拟——人体模型(HBM)

IEC61340-3-2:静电影响模拟方法——静电放电模拟——机器模型(MM)

IEC61340-3-3:静电影响模拟方法——静电放电模拟——带电器件模型(CDM)

IEC61340-4-1:特别应用的测试——安装地板及地面覆盖物的静电特性

IEC61340-4-2:待考虑

IEC61340-4-3:特别应用的测试——防静电鞋类的特性

IEC61340-5-1:电子器件的静电保护——一般性要求

IEC61340-5-2:电子器件的静电保护——用户指南

ESD敏感度测量标准:

ANSI/ESD STM5.1人体模型

ANSI/ESD STM5.2机器模型

ANSI/ESD STM5.3.1组件充电模型

ANSI/ESD SP5.3.2

ANSI/ESD SP5.4

ANSI/ESD SP5.5.1

|

模型 |

规范 |

备注 |

|

|

芯片级 |

人体放电模式工业测试标准 |

MIL-STD-883C method 3015.7 ANSI-STM5.1-2001 JESD22-A114D-2005 AEC-Q100-002D-2003 IEC61340-3-1 |

人体的等效电容定为100pF,人体的等效放电电阻定为1.5KΩ |

|

机器放电模式工业测试标准 |

EIAJ-IC-121 method20 ANSI-STM5.2-1999 JESD22-A115-A-1997 AEC-Q100-003E-2003 IEC61340-3-2 |

等效电阻为0Ω,其等效电容为200pF |

|

|

组件充电模式工业测试标准 |

JESD22-C101-C ESD DS5.3.1 AEC-Q100-011B -2003 |

IC对地等效电容各异,没有统一模型参数 |

|

|

电场感应模式工业测试标准 |

JESD22-C101-C |

||

|

TLP(Transmission Line Pulse) |

ESD SP5.5.1-2004 |

TLP测试可以用来代替人体模型中的双指数波形对设备进行抗扰度测试,通过对元件失效机理的分析,可以得出静电放电脉冲注入到元件内的能量是导致元件失效的主要因素 |

|

|

系统级 |

人体-金属模型(Body-Metal Model),也叫场增强模型(静电枪模型) |

IEC801-2 IEC1000-4-2 IEC61000-4-2 |

系统级测试标准,模型的储能电容为150pF(包括发生器和受试设备、接地参考平面以及耦合板之间的分布电容);放电电阻为330Ω,用以代表人手握金属时的人体电阻;充电电阻为50~100MΩ。 |

在对电火工品进行静电敏感度测试时,根据MIL-STD-1512采用的HBM的参数为电容500pF,电阻5kΩ;在汽车行业中,HBM参数为电容330pF,电阻2kΩ。

3、ESD等级及测试

ESD测试结果的评判等级分为芯片级和系统级,具体定义如下表所示:

|

芯片级 |

系统级 |

||||||||

|

HBM |

MM |

CDM |

接触放电(Contact Discharge) |

空气放电(Air Discharge) |

|||||

|

等级 |

测试电压/KV |

等级 |

测试电压/KV |

探头类型 |

等级 |

测试电压/KV |

探头类型 |

||

|

Okey |

±2 |

±0.2 |

±1 |

1 |

±2 |

尖头探头 |

1 |

±2 |

圆头探头(为了防止电荷泄漏),15KV以上用球形放电头 |

|

Safe |

±4 |

±0.4 |

±1.5 |

2 |

±4 |

2 |

±4 |

||

|

Super |

±10 |

±1 |

±2 |

3 |

±6 |

3 |

±8 |

||

|

4 |

±8 |

4 |

±15 |

||||||

|

x |

特殊 |

x |

特殊 |

||||||

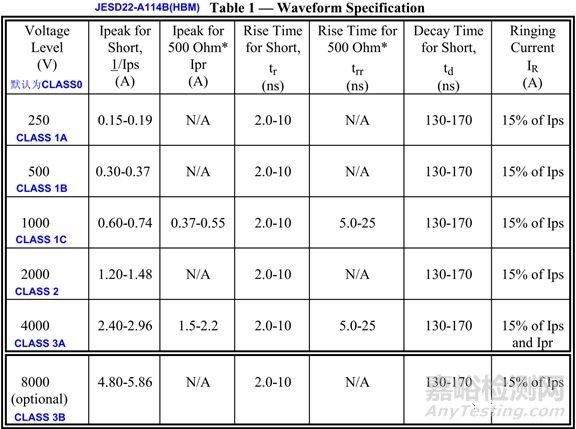

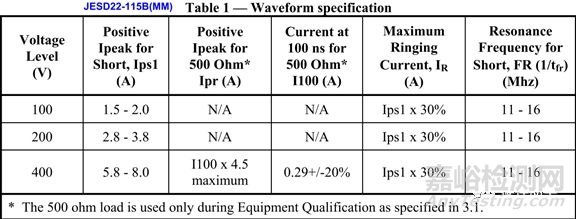

芯片级测试波形参数如下所示 :

3.1、系统级测试方法

系统级ESD测试中,接触放电是首选的测试方法,也就是说在相同的放电电压情况下,接触放电的严格度远大于空气放电。

特例:某些情况下,如键盘的金属导电部分藏在绝缘层覆盖下,及设备螺钉的金属部分有时可见不可及,此时就不得不用空气放电测试。

接触放电:

放电对象(位置)

放电等级

判断标准

放电方法

放电导线与枪头同时放在被测端子(表面)上,进行连续放电,放电间隔时间应不少于1秒;

先用枪头对被测端子(表面)放电,然后将枪头移开,再用放电导线对被测端子(表面)的电荷导入大地。

如果上述两种测试方法的结果不同时,应以恶劣的结果为准。

空气放电:

放电对象(位置)

放电等级

判断标准

放电方法:枪头紧贴绝缘件的表面,绝缘件之间的缝隙滑行,如在某点出现放电现象(可能是对绝缘表面下的非绝缘器件放电),则需对该点放电10次。(对无放电现象发生的表面,无需进行10次放电操作)无需对水平、垂直金属板进行放电操作。

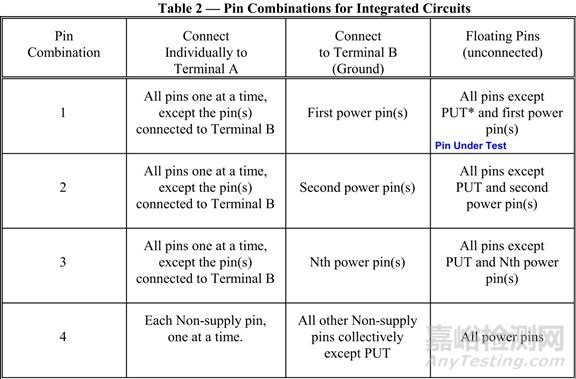

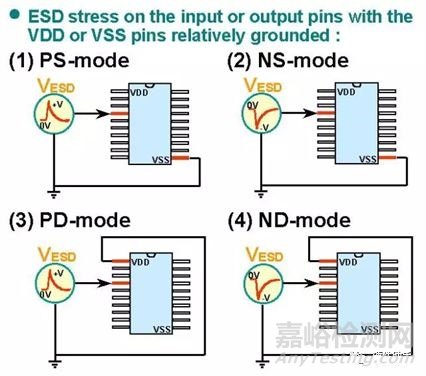

3.2、芯片级测试方法

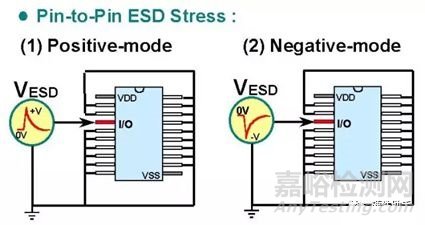

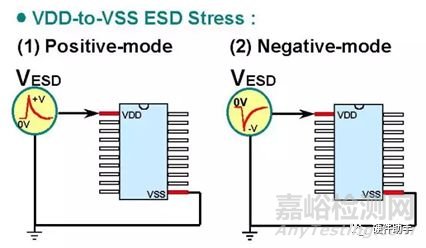

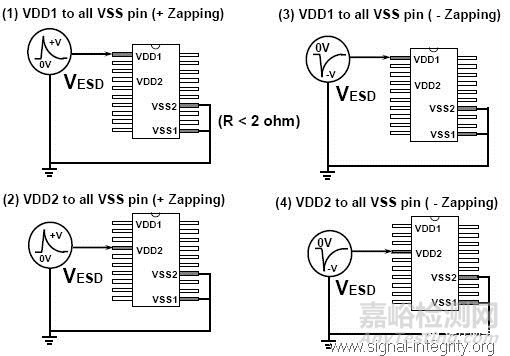

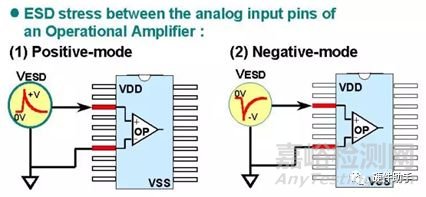

芯片级的测试,静电加在引脚之间,各种引脚可以进行组合,详细见下:

加在I/O口和VDD/VSS之间

加在pin和pin之间

加在VDD和VSS之间

加在多个VSS和VDD之间

加在模拟引脚之间

4、ESD防护

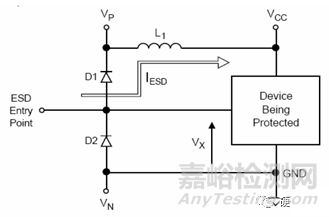

ESD防护器件的一般连接方式如下图所示:

4.1、系统级防护

系统级防护主要就是增加板级ESD防护器件,具体可参见之前的文章《防护类器件介绍》。

选择ESD器件应该遵循下面的要求:

选择静电保护器件是应注意钳制电压不要超过受保护器件的最大承受电压;

电路电压不超过保护器件工作电压;

低电容值、漏电流尽可能的减少干扰及损耗;

静电保护器件尽量安装在最接近静电输入的地方,远离被保护器件;

静电保护器件一定接的是大地,不是数字地;

尽可能的用Vcc和地平面充当电源和地分散能量;

回地的线路尽量的短,静电保护器件与被保护线路之间的距离尽量的短;要确保印刷电路上的走线从ESD保护二极管阵列的Vp和Vn到Vcc和地平面间走线尽量地短、宽。理想情况是,将Vp和Vn直接通过多个过孔接到Vcc和地平面;

在Vp和地平面间连入一个高频旁路电容——用最短的走线使自感最小;

尽量避免被保护与未被保护线路并排走线。

4.2、芯片级防护

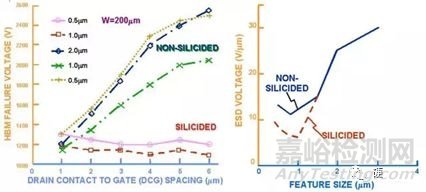

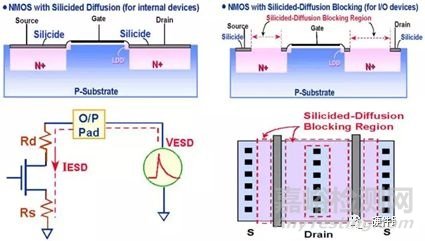

随着器件尺寸越来越小,结深越来越浅,GOX(栅氧化层)越来越薄,所以静电击穿越来越容易,而且在高级制程里面,Silicide引入也会让静电击穿变得更加尖锐,所以几乎所有的芯片设计都要克服静电击穿问题。

静电放电保护可以从FAB端的Process解决,也可以从IC设计端的Layout来设计,所以你会看到Process有一个ESD的option layer,或者Design rule里面有ESD的设计规则可供客户选择等等。当然有些客户也会自己根据SPICE model的特性通过layout来设计ESD。

4.2.1、制程上的ESD

制程上解决ESD问题,要么改变PN结,要么改变PN结的负载电阻,而改变PN结只能靠ESD_IMP了,而改变PN结的负载电阻,就是用non-silicide或者串联电阻的方法了。

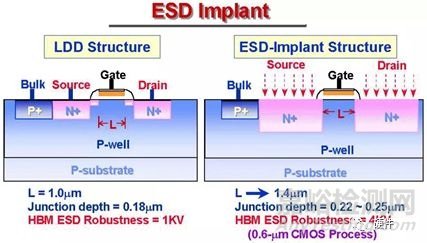

Source/Drain的ESD implant:因为LDD结构在gate poly两边很容易形成两个浅结,而这个浅结的尖角电场比较集中,而且因为是浅结,所以它与Gate比较近,所以受Gate的末端电场影响比较大,所以这样的LDD尖角在耐ESD放电的能力是比较差的(<1kV),所以如果这样的Device用在I/O端口,很容造成ESD损伤。所以根据这个理论,需要一个单独的器件没有LDD,但是需要另外一道ESDimplant,打一个比较深的N+_S/D,这样就可以让那个尖角变圆而且离表面很远,所以可以明显提高ESD击穿能力(>4kV)。但是这样的话这个额外的MOS的Gate就必须很长防止穿通(punch through),而且因为器件不一样了,所以需要单独提取器件的SPICE Model。

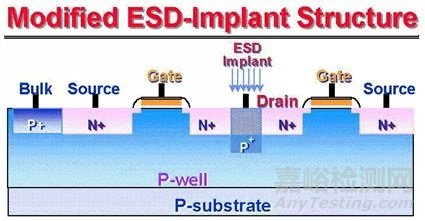

接触孔(contact)的ESD implant:在LDD器件的N+漏极的孔下面打一个P+的硼,而且深度要超过N+漏极(drain)的深度,这样就可以让原来Drain的击穿电压降低(8V→6V),所以可以在LDD尖角发生击穿之前先从Drain击穿导走,从而保护Drain和Gate的击穿。所以这样的设计能够保持器件尺寸不变,且MOS结构没有改变,故不需要重新提取SPICE model。当然这种只能用于non-silicide制程,否则contact你也打不进去implant。

SAB (SAlicide Block):一般为了降低MOS的互连电容,会使用silicide/SAlicide制程,但是这样器件如果工作在输出端,器件负载电阻就会变低,外界ESD电压将会全部加载在LDD和Gate结构之间很容易击穿损伤,所以在输出级的MOS的Silicide/Salicide通常会用SAB(SAlicide Block)光罩挡住RPO,不要形成silicide,增加一个photo layer成本增加,但是ESD电压可以从1kV提高到4kV。

串联电阻法:这种方法不用增加光罩,应该是最省钱的了,原理有点类似第三种(SAB)增加电阻法,故意给他串联一个电阻(比如Rs_NW,或者HiR,等),这样也达到了SAB的方法。

4.2.2、设计上的ESD

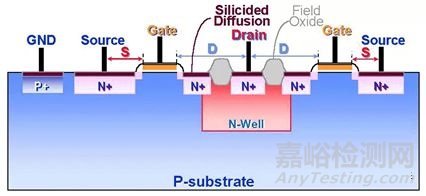

这完全靠设计者的功夫,有些公司在设计规则就已经提供给客户solution了,客户只要照着画就行了,有些没有的则只能靠客户自己的designer了,很多设计规则都是写着这个只是guideline/reference,不是guarantee的。一般都是把Gate/Source/Bulk短接在一起,把Drain结在I/O端承受ESD的浪涌(surge)电压,NMOS称之为GGNMOS(Gate-Grounded NMOS),PMOS称之为GDPMOS(Gate-to-Drain PMOS)。

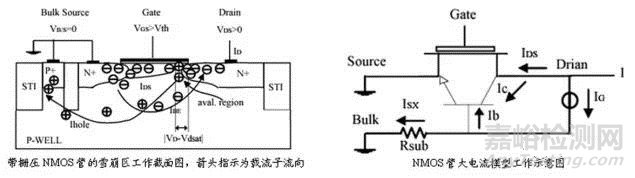

以NMOS为例,原理都是Gate关闭状态,Source/Bulk的PN结本来是短接0偏的,当I/O端有大电压时,则Drain/Bulk PN结雪崩击穿,瞬间bulk有大电流与衬底电阻形成压差导致Bulk/Source的PN正偏,所以这个MOS的寄生横向NPN管进入放大区(发射结正偏,集电结反偏),所以呈现Snap-Back特性,起到保护作用。PMOS同理推导。

本文主要介绍了ESD的相关模型及测试标准、测试结果及判定、ESD相关防护等。ESD防护可以参见《防护类器件介绍》中的相关部分。

来源:硬件助手