您当前的位置:检测资讯 > 科研开发

嘉峪检测网 2025-09-28 18:58

导语:在现代电子设备中,存储单元扮演着至关重要的角色,从手机消费品、工业设备、汽车电子、医疗设备、几乎都有一颗甚至多颗“记忆体”。然而,这些设备产品中的存储单元(Flash、SRAM、DRAM、ROM等)可能会发生”无缘无故”的失效。特别是对于户外高海拔装置、航天控制系统,辐射对其影响不容忽视。本文将探讨辐射对存储器件的失效影响,分析其机理,并提出相应的改进措施。

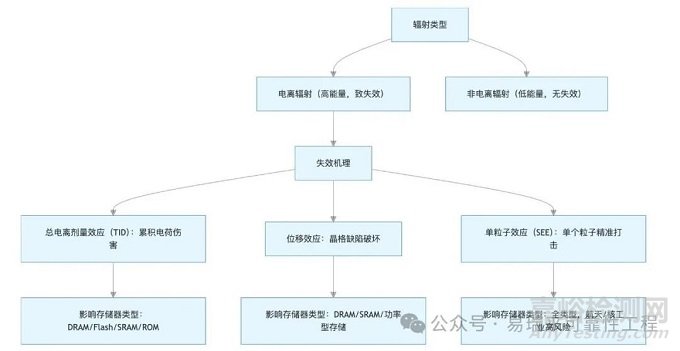

一、辐射类型

要理解辐射对存储器件的影响,首先需明确辐射的核心分类标准—— 根据能量是否能使物质原子发生电离,辐射可分为两大类,且只有特定类型的辐射会导致存储器件失效。

1.1 电离辐射(存储失效的 “主因”)

定义:能量高于物质原子电离能(通常>10eV),能使原子中的核外电子脱离原子核束缚,形成带电离子的辐射。

常见类型:γ 射线、X 射线、高能电子(β 射线)、中子、重离子(如质子、氦离子)等。

关键特性:能量高、穿透力强,既能改变存储器件的电子态(如产生电荷积累),也能破坏原子排列(如导致晶格移位),是引发存储器件失效的核心辐射类型。

图1 辐射引发SRAM FPGA失效

1.2 非电离辐射(无存储失效风险)

定义:能量低于物质原子电离能,无法使原子电离,仅能引发原子振动加剧或电子能级跃迁(电子不脱离原子核)的辐射。

常见类型:射频、红外线、可见光、微波等。

关键特性:能量低、作用温和,既无法在存储器件中产生电离电荷,也不能将晶格原子“撞出原位”,因此几乎不会导致存储器件和其它器件的辐射失效。

二、电离辐射引发的存储失效机理:三类核心“伤害路径”

电离辐射对存储器件的失效影响,通过三种独立且明确的机理实现—— 总电离剂量效应(TID)、位移效应(DD)、单粒子效应(SEE)。这三类机理均由电离辐射引发,但作用方式、影响特点完全不同,逐一说明如下:

2.1 总电离剂量效应(TID):“累积的电荷伤害”

2.1.1 定义与机理

总电离剂量(Total Ionizing Dose,TID):指电离辐射在存储器件材料(如硅、氧化层)中产生的“总电离电荷密度”,单位通常为 krad (Si)(每克硅吸收辐射能量对应的电离电荷)。

失效机理:电离辐射(如γ 射线、X 射线)照射时,会在器件的 “氧化层”(如 MOS 管栅氧化层、存储电容介质层)中产生大量 “电子 - 空穴对”。其中,电子迁移速度快,会迅速被电极收集;但空穴迁移慢,易被氧化层缺陷 “困住”(形成 “氧化层陷阱电荷”),或在氧化层与硅衬底界面形成 “界面态”。随着辐射剂量累积,这些电荷和界面态会形成 “寄生电场”,改变器件电学特性。

2.1.2 对不同存储器的失效影响

|

存储器类型 |

TID 导致的典型失效 |

核心影响机理 |

|

DRAM(动态随机存取存储器) |

刷新周期缩短、数据保持时间变短、漏电流增大 |

栅氧化层陷阱电荷使MOS 管阈值电压降低,存储电容电荷泄漏加速,需更频繁刷新才能保住数据 |

|

NAND Flash(闪存) |

编程/ 擦除(P/E)次数减少、阈值电压窗口缩小、数据保存时间下降 |

隧道氧化层陷阱电荷阻碍电子隧道注入/ 抽出,导致编程失败;界面态加剧漏电,缩短数据 retention 时间 |

|

SRAM(静态随机存取存储器) |

静态功耗上升、读写错误率增加、闩锁效应风险提高 |

界面态恶化MOS 管亚阈值特性,产生额外漏电;阈值电压偏移导致存储单元无法稳定保持 “0/1” |

|

ROM(只读存储器) |

输出电平漂移、部分存储位“翻转” |

氧化层累积电荷改变器件导通特性,高电平位可能因漏电变为低电平 |

2.1.3 关键特点

累积性:即使单次辐射剂量低,长期照射后总剂量达到阈值(商用器件通常10-100 krad (Si),航天级需>1000 krad (Si)),仍会导致永久失效;

普遍性:所有依赖氧化层/ 介质层的存储器均受影响,无 “豁免类型”。

2.2 位移效应(DD):“晶格缺陷的破坏”

2.2.1 定义与机理

位移效应(Displacement Damage):指电离辐射中的“高能粒子”(如中子、重离子)撞击存储器件半导体晶格,使晶格原子脱离原位置,形成 “空位 - 间隙原子对”(弗伦克尔缺陷)的失效机理。

失效逻辑:高能粒子的动量传递给晶格原子,使其获得足够能量“跳出” 平衡位置 —— 空位(原子离开后的空缺)和间隙原子(脱离原位的原子)会成为 “载流子障碍”:要么阻碍电子 / 空穴运动,降低载流子迁移率;要么改变存储单元的电荷存储能力,最终破坏 “0/1” 数据状态。

2.2.2 对不同存储器的失效影响

|

存储器类型 |

DD导致的典型失效 |

核心影响机理 |

|

DRAM |

存储电容漏电加剧、刷新失败 |

晶格缺陷使电容介质层出现“漏电通道”,电荷无法稳定保存 |

|

SRAM |

静态电流激增、逻辑状态翻转 |

缺陷作为载流子复合中心,导致MOS 管导通特性异常,存储单元无法保持稳定状态 |

|

可编程存储器件(如EEPROM) |

编程电压阈值升高、擦除不完全 |

晶格缺陷阻碍电荷在浮栅与衬底间的转移,导致编程/ 擦除操作失效 |

2.2.3 关键特点

瞬时性:单次高能粒子撞击即可产生缺陷,无需剂量累积;

针对性:对晶格结构敏感的存储器(如DRAM、SRAM)影响更显著,对无晶格依赖的器件(如部分新型闪存)影响较弱。

2.3 单粒子效应(SEE):“单个粒子的精准打击”

2.3.1 定义与机理

单粒子效应(Single Event Effect,SEE):指电离辐射中“单个高能粒子”(如重离子、质子)穿过存储器件时,在局部区域产生大量电子 - 空穴对,引发器件逻辑状态异常或功能失效的机理。

失效逻辑:单个高能粒子(能量通常>MeV)在器件中形成 “电荷轨迹”,局部电荷密度极高 —— 若这些电荷被存储单元(如 SRAM 的触发器、DRAM 的电容)收集,会瞬间改变单元的电荷平衡:例如 SRAM 中触发器的 “0” 状态被瞬间 “冲翻” 为 “1”,DRAM 电容中的电荷被瞬间中和,导致数据错误。

2.3.2 SEE 的主要类型及对存储器的影响

SEE 并非单一失效模式,根据影响程度可分为 “软失效”(可恢复)和 “硬失效”(永久损坏):

|

SEE 类型 |

定义 |

对存储器的影响 |

恢复情况 |

|

单粒子翻转(SEU) |

单个粒子导致存储单元数据“0→1” 或 “1→0” |

DRAM/SRAM 数据错误、Flash 编程位错误 |

重新写入正确数据即可恢复(软失效) |

|

单粒子锁定(SEL) |

粒子引发器件内部形成低阻通路,电流激增 |

存储芯片过热、烧毁,甚至牵连整个电路 |

需断电重启,严重时导致永久损坏(半硬失效) |

|

单粒子烧毁(SEB) |

粒子导致功率器件(如存储芯片的供电管)击穿 |

存储芯片供电电路损坏,无法供电 |

永久失效,需更换器件 |

|

单粒子擦除(SEE) |

粒子导致Flash 浮栅上的电荷瞬间丢失 |

存储数据被意外擦除 |

重新编程可恢复数据,但器件无损坏(软失效) |

2.3.3 关键特点

随机性:粒子撞击位置、时间不可预测,失效具有偶发性;

高风险场景:航天(宇宙射线中的重离子)、核工业(辐射源附近)等场景中,SEE 发生概率显著升高。

三、存储器件抗辐射失效的措施:多层级防护体系

针对上述三类失效机理,从“器件设计 - 制造工艺 - 系统应用” 三个层面构建防护体系,覆盖不同辐射场景需求:

3.1 器件设计:从 “源头” 提升抗辐射能力

3.1.1 针对 TID 的设计优化

氧化层加固:采用“高纯度氧化层制备工艺”(如原子层沉积 ALD),减少氧化层中的初始缺陷,降低陷阱电荷产生概率;

界面态抑制:在氧化层与硅衬底间引入“氮化物缓冲层”,减少辐射引发的界面态生成。

3.1.2 针对位移效应的设计优化

晶格结构强化:采用“应变硅技术”,通过应力增强晶格原子间的结合力,减少粒子撞击导致的原子移位;

冗余晶格设计:在存储单元周围设置“备用晶格区域”,即使部分晶格出现缺陷,也可通过电路切换启用备用区域。

3.1.3 针对 SEE 的设计优化

抗SEU 存储单元:SRAM 采用 “双互锁存储单元(DICE)”,通过 4 个晶体管形成交叉反馈结构,单个粒子撞击无法改变状态;DRAM 增加 “电荷冗余电容”,提高抗电荷扰动能力;

SEL 防护电路:在存储芯片供电端串联“电流限制器”,一旦发生 SEL 导致电流激增,立即切断供电,避免器件烧毁。

3.2 制造工艺:减少 “先天缺陷”

抗辐射材料选用:采用“高纯度硅片”(杂质含量<10¹⁵ atoms/cm³),减少辐射引发缺陷的 “靶点”;Flash 的隧道氧化层采用 “多层氧化 - 氮化 - 氧化(ONO)结构”,提升抗电荷陷阱能力;

工艺参数优化:离子注入过程中控制“低能量、低剂量”,减少注入对晶格的损伤;退火工艺采用 “快速热退火(RTA)”,消除制造过程中产生的初始晶格缺陷。

3.3 系统应用:“后天补救” 降低失效影响

3.3.1 软件层面

错误检测与纠正(EDAC):在存储系统中集成“汉明码”“BCH 码” 等纠错电路,实时检测 SEU 导致的数据错误并自动纠正;对重要数据采用 “三重校验码”,提升纠错能力;

定期数据刷新:针对TID 导致的 DRAM 数据保持时间缩短,通过软件设置 “动态刷新周期”,根据辐射环境强度调整刷新频率。

3.3.2 硬件层面

辐射屏蔽:在存储器件外部设置“重金属屏蔽层”(如铅、钨合金),削弱 γ 射线、X 射线的穿透力;航天场景中采用 “多层屏蔽结构”(铝 + 聚乙烯),同时屏蔽重离子和中子;

冗余设计:采用“三模冗余(TMR)”—— 三个相同存储模块同时存储数据,通过 “多数表决” 输出正确结果,即使一个模块因 SEE 失效,也不影响系统运行;重要数据采用 “冷热备份”,主存储失效时立即切换至备份存储。

结语:随着技术的发展,新型存储器如MRAM、RRAM和FRAM展现出比传统SRAM和DRAM更好的抗辐射特性,在航空航天和核工业等辐射环境中具有广阔应用前景。

来源:易瑞来可靠性工程