您当前的位置:检测资讯 > 科研开发

嘉峪检测网 2021-06-17 13:08

EMC设计时候需要考虑的有3点,如下所述。

1. EMC的设计与产品本身性能以及机能是同样重要的,noise的低减其实就等同于我们产品的性能提高了,二者是相辅相成的关系。

2. 先期导入式的设计

EMC的设计应该在产品的初期设计阶段导入进来,因为伴随着项目开发的推进,可能运用的noise降低的技术方法就会因为整个项目周期和预算的束缚,采用的种类越来越少,同时对策产生的成本会越来越高。所以从QCD的开发前提上考虑,务必将EMC的设计放在设计初期(产品设计构想阶段),这个阶段的成本,开发工数以及技术运用手段都是最高效的。

3. 产品整体的EMC设计

这是所指的EMC设计包含机构设计+回路设计+PCB基板设计+电子芯片的选定与设计+内部模块的设计(GPS/BT 模块等)+软件设计+生产技术等。

上记设计环节是紧密联系,相辅相成的,缺一不可。

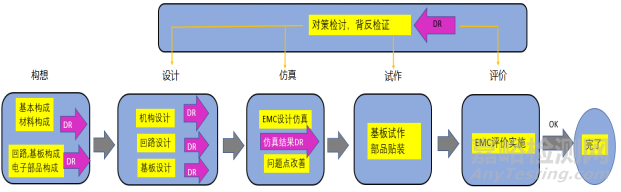

我们一般采取的设计流程如下:

今天主要想介绍的是关于电子部品选定的EMC设计的相关注意事项

一 部品的选定

对于一个电子设备而言,电路设计是保证电磁兼容特性的最基本的内容,电路设计的缺陷很难通过其他方法进行弥补,即使可以的话也要付出较高的成本来解决。

那么进行电路设计前,我们应该如何选定相关的电子部品呢?

1.电子IC部品本身的EMC设计是否有所考虑

a.我们在选定电子部品的时候,需要仔细阅读他们的datasheet手册,事前与厂家确认是否有针对EMC的设计组入到产品中,一般来说国际知名的电子元器件厂家都会通过他们的测试板来验证相关IC的EMC性能。同时我们作为IC的使用方也可以先发制人,把我们的应用场景和EMC的相关标准告知厂商,让他们进行前期的验证和检讨,这样可以大大缩减我们的开发周期。

比如:器件是否有很好的抗干扰性,耐ESD特性

器件的内部,数字部分和模拟部分是否有隔离设置

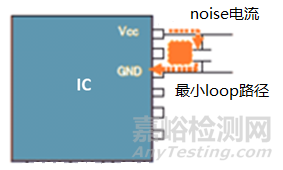

2.电源与GND之间的去耦电容的配置

尽可能选择电源引脚和地引脚位于封装中心并且相邻位置的器件,这样可以减小loop路径

例如:信号或者电源与GND之间的return路径是否采用了最小loop配置

(通常是5mm以内配线长利用)

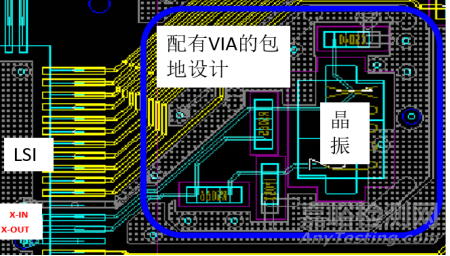

3.晶振周边的GND配置推荐(通过过孔和包地的方式把晶振围起来,防止noise对外的辐射)

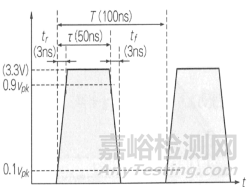

4. IC出力侧一般采用最小的slew rate以及驱动能力的设计

(选择逻辑状态改变时所需要输入电流跟小的器件)

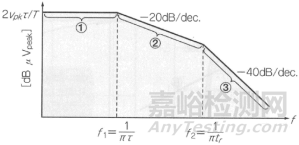

信号的上升沿和下降沿过快的情况下很容易产生高频noise,同时驱动电流过大也很容易产生noise。如下图所示,上升沿下降沿的时间越快,那么高频noise的衰减就越慢。

5. DCDC电源IC的选定

我们通常考虑选定的是具有软件散频的DCDC电源IC.

扩谱技术(软件散频)近年来越来越多的被设计者所使用,原理主要是基于傅里叶变化,周期性的脉冲信号经过傅里叶变换后可以得到一系列离散的谱线,脉冲信号上的能量也就主要集中在这些谱线的频率上了,而扩谱技术正式基于这一点应用在电路上,让时钟电路的频率发生抖动,从而使得周期性的脉冲信号变为非周期的脉冲信号,由于非周期的脉冲的频谱是连续的,产生的能量会分布在所有的频率上,从而某个特定频率上的能量就会有所降低,通常我们测试使用的接收机的带宽是固定频率的,所以在测试的时候,有一部分能量就会落在接收机带宽的范围以外,进而可以通过测试。

使用前提:

a.这个只是为了从节约成本的角度单纯为了通过国标实验或者企业标准实验的一个方法。如果接收机的带宽大于扩谱后的带宽的情况下, 我们还是要通过滤波或者屏蔽来解决这个问题。

b.同时扩谱后的工作频率也要满足IC输入端的规格要求,超出规格后,系统的工作可能会异常或者不工作。

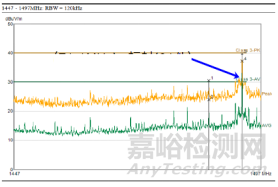

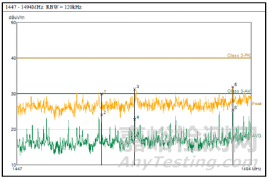

如上图所示,1493.1Mhz的频段超出规格值6db, 经过分析我们产品的LVDS输出侧clock的21倍频(71.1Mhz*21=1493.1Mhz),而这段测试频率的范围是(1447-1494),我们调整频率的方法将LVDS的clock调整为71.3Mhz(71.3Mhz*21=1497.3Mhz),恰好落到了1494的外面,进而通过了测试。

备注:通常我们在开发前期,会做一份倍频表的资料,包含下面内容

a. 各个模块下使用的晶振的基频/LVDS,I2C,I2S,等通信信号的基频等

b. 将每个基频的30倍以内的倍频分别计算出来(1倍频至30倍频)

c. 将要测试的频段也全部罗列出来

综上所述,准备好上记资料后我们在遇到问题频点的时候,就为我们尽快排查问题提供了帮助。6. DCDC 电源IC中升压降压电感器件的选择。

开磁类型的电感在我们选择的时候,往往从电感产生的noise会有所增加。因此为了降低对外辐射的noise,我们通常选用闭此类型的电感应用在回路中(村田,罗姆,顺络等)

例如:DD1217AS-H-100M=P(10μ)(東光)

SWPA5040S100MT(10μ)(Sunlord)

来源:电磁兼容EMC