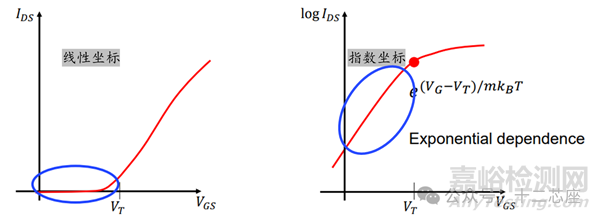

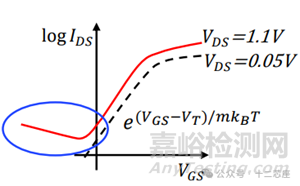

在亚阈值区,若以对数尺度绘制其曲线,会呈现出线性关系,具体遵循自然对数规律(即ln(ex)=x)。这一现象表明,在达到阈值电压(VT)之前,亚阈值传导(或漏电流)在自然状态下呈指数变化。

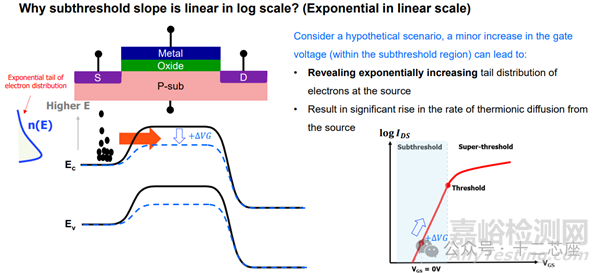

为什么阈下斜率在对数尺度下是线性的?(线性指数)

门电压的轻微增加(在阈下区域内)

电子在源极处的指数级增长导致从源极的热电子扩散速率显著上升.

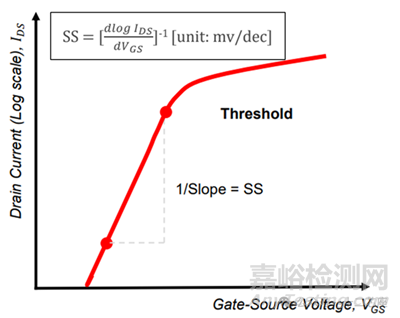

Subthreshold Swing (SS)SS:

增加或减少id 10倍 (一个数量级) 所需的栅极电压, SS由对数IDS与VGS斜率的倒数给出。

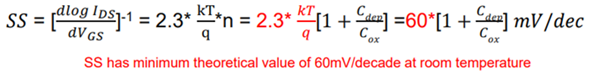

那么,SS 有哪些影响因素?

温度,温度升高,SS 增大。

栅氧化层电容增大,SS 减小;使用high k介质,减小栅氧化层厚度,都可以使 SS 减小。

Si耗尽层电容减小,SS 减小;使耗尽层宽度增大的因素,例如衬底浓度Na减小,衬底偏置电压增大,会使 SS 减小。

栅氧化层和衬底硅界面会存在一些界面缺陷,能存放电荷,这些缺陷的增加,相当于叠加了一个电容,会使 SS 增大。

沟道长度较小会使得栅控能力减弱, SS 增大。

栅电压增大,随着表面反型增强,栅对channel的控制能力就越弱,SS 增大。

其最小可实现值又是多少?

但一些新型器件,如隧穿器件(TunnelingTransistor)以及负电容器件,可以获得低于此理论值的亚阈值摆幅。

Subthreshold LeakageLeakage

current mechanism-沟道穿通效应-punch through

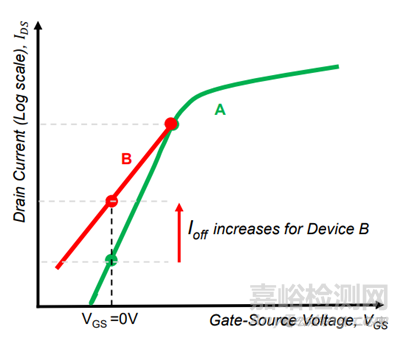

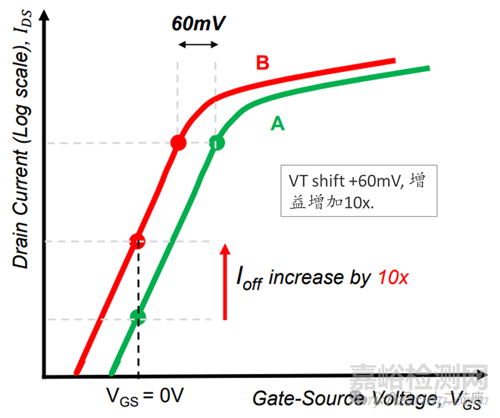

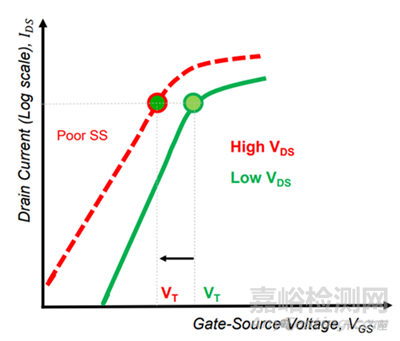

在相同的阈值电压下,与A相比,B在亚阈值斜率(SS)上表现得更差。较小的SS(即更陡峭的斜率)对于将关态泄漏降至最低至关重要。

A 和 B 都具有类似的SS,然而,B在VGS=0V时的漏电是A的十倍。

因此在相同的SS下,为了降低动态功率,缩放其VDD。curve右移,Ioff降低。

DIBL

Drain Induced Barrier Lowering (DIBL)

知识日记:DIBL, Drain Induced Barrier Lowering, 漏致势垒降低效应

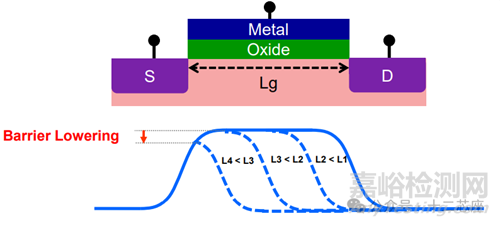

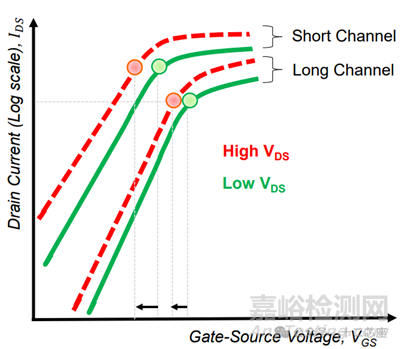

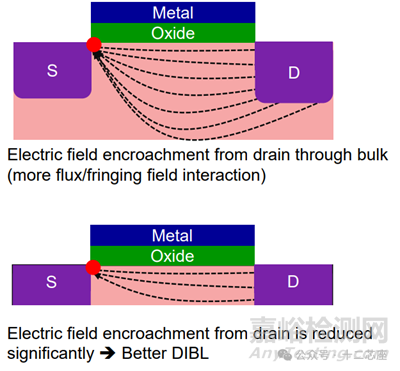

来自漏极的场强降低了源极处的电子注入势垒,在栅极长度较短的器件中(在 VDS = 0 时)观察到的影响更为显著。

漏极电场向沟道的侵入会降低源端电子注入势垒,从而导致阈值电压(VT)下降。该效应受以下因素加剧:

沟道(栅极)长度(Lg)缩短

漏源电压(VDS)升高

栅极逐渐失去对沟道的控制,而漏极的影响逐渐增强,上述机制还会使关态漏电流(Ioff)上升,并使亚阈值斜率(SS)恶化。

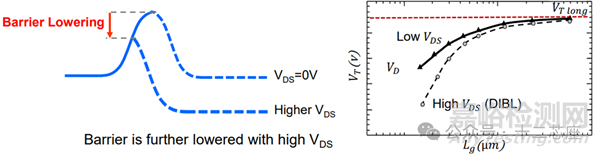

漏极感应势垒降低(DIBL)会在漏源电压 VDS 升高时使阈值电压 VT 下降。

DIBL 系数 = ΔVT / ΔVDS

单位:mV/V

该系数定量描述每单位 VDS 上升所引起的 VT 降低量;理想情况下应为 0。

DIBL 还会使亚阈值斜率(SS)变差,即其数值增大。

Short Channel Effect (SCE)

Vtsat, Vtlin, Vtgm:三种MOSFET阈值电压对比

沟道越短,漏极电场向源端的穿透就越强;

因此,短沟道器件会表现出更显著的 DIBL 漂移。

当器件体区减薄时,漏极电场向源端穿透的程度会因体区耗尽区的“挤压”而减弱,从而抑制 DIBL。

为进一步改善 DIBL,还可采用以下工艺/结构策略:

浅结源/漏(Shallow S/D junctions),

晕环(Halo)与倒阱(Retrograde wells)离子注入。

GIDL

Gate Induced Drain Leakage (GIDL)

知识日记:GIDL, Gate Induced Drain Leakage, 栅致漏极泄漏电流

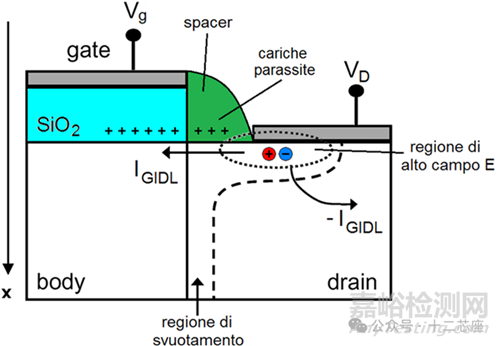

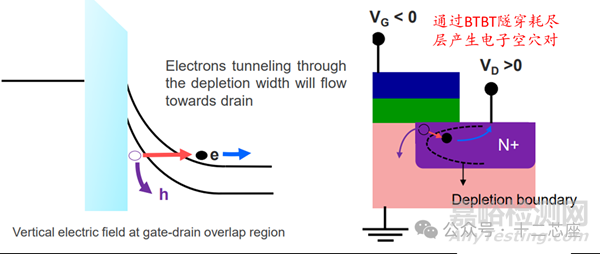

栅极感应漏极漏电流(GIDL)通常发生在栅极被偏置到积累区、同时漏极被施加反向高电压的情形下。

此时,在栅-漏(N+)重叠区域,器件被迫进入深耗尽状态:栅极处于积累偏压,漏极处于反向偏置。

栅-漏重叠区内跨越栅氧的强垂直电场使价带中的电子发生带-带隧穿,跃迁至导带,从而产生 GIDL。

免责声明:作者尊重知识产权、部分图片和内容来源于公开网络,版权归原撰写发布机构所有,如涉及侵权,请及时联系删除。

Reference:

1. Fundamental of Modern VLSI Devices, Yuan Taur and Tak H. Ning

2. Modern Semiconductor Devices for Integrated Circuits, Chenming Hu

3. Semiconductor Fundamentals, Robert F. Pierret

4. Semiconductor Physics and Devices, Donald Neamen

5. Physics of Semiconductor Devices, Simon Sze6. Micron