您当前的位置:检测资讯 > 科研开发

嘉峪检测网 2025-08-25 13:37

不断增长的 AI GPU 集群之间对通信的极高需求,正推动着人们转向使用光进行跨网络层通信。今年早些时候,Nvidia 宣布其下一代机架级 AI 平台将采用硅光子互连技术与共封装光学器件 (CPO),以实现更高的传输速率和更低的功耗。在今年的 Hot Chips 大会上,Nvidia 发布了有关其下一代 Quantum-X 和 Spectrum-X 光子互连解决方案的更多信息,并透露了它们将于 2026 年上市。

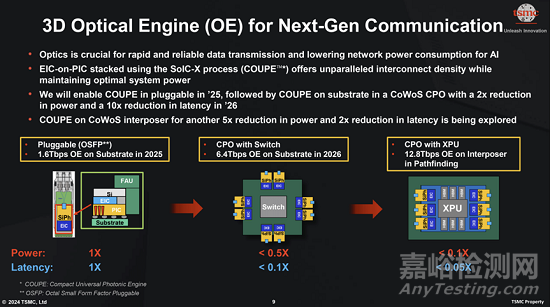

Nvidia 的路线图很可能与台积电的 COUPE 路线图紧密相关,后者分为三个阶段。第一代是用于 OSFP 连接器的光学引擎,可提供 1.6 Tb/s 的数据传输率,同时降低功耗。第二代将采用 CoWoS 封装技术,并采用同封装光学器件,在主板级别实现 6.4 Tb/s 的数据传输率。第三代的目标是在处理器封装内实现 12.8 Tb/s 的数据传输率,并进一步降低功耗和延迟。

为什么是 CPO?

在大规模 AI 集群中,数千个 GPU 必须像一个系统一样运行,这给这些处理器的互连方式带来了挑战:每个机架不再拥有自己的一级(架顶式)交换机,并通过短铜缆连接,而是将交换机移至机架末端,以便在多个机架之间创建一致、低延迟的结构。这种迁移极大地延长了服务器与其第一个交换机之间的距离,这使得铜缆在 800 Gb/s 这样的速度下变得不切实际,因此几乎每个服务器到交换机以及交换机到交换机的链路都需要光纤连接。

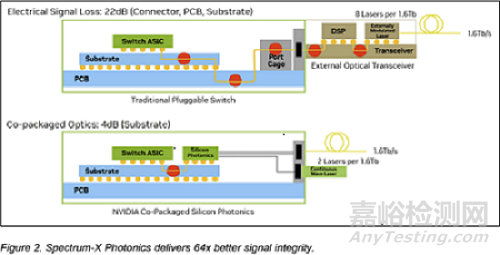

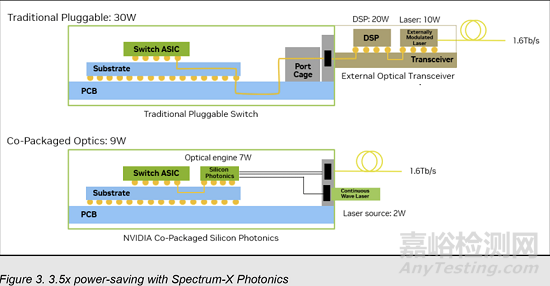

在这种环境下使用可插拔光模块存在明显的局限性:此类设计中的数据信号离开ASIC,穿过电路板和连接器,然后才转换为光信号。这种方法会产生严重的电损耗,在200 Gb/s通道上损耗高达约22分贝,这需要使用复杂处理进行补偿,并将每个端口的功耗增加到30W(这又需要额外的冷却并造成潜在的故障点)。据Nvidia称,随着AI部署规模的扩大,这种损耗几乎变得难以承受。

CPO 通过将光转换引擎与交换机 ASIC 并排嵌入,避免了传统可插拔光模块的缺点,信号无需通过长距离电气线路传输,而是几乎立即耦合到光纤中。因此,电气损耗降低至 4 分贝,每端口功耗降至 9W。这种布局省去了众多可能出现故障的组件,并大大简化了光互连的实施。

Nvidia 声称,通过放弃传统的可插拔收发器,并将光学引擎直接集成到交换机芯片中(得益于台积电的 COUPE 平台),其在效率、可靠性和可扩展性方面实现了显著提升。Nvidia 表示,与可插拔模块相比,CPO 的改进非常显著:功率效率提高了 3.5 倍,信号完整性提高了 64 倍,由于有源设备减少,弹性提高了 10 倍,并且由于服务和组装更简单,部署速度提高了约 30%。

以太网和 InfiniBand 的 CPO

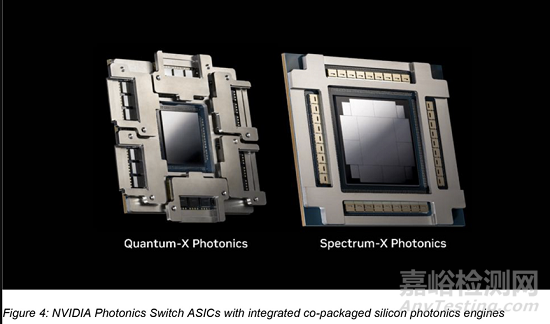

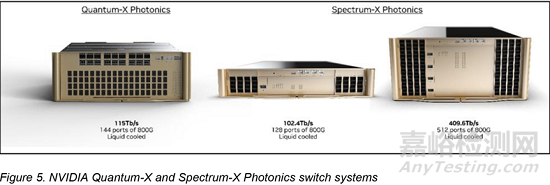

Nvidia 将推出基于 CPO 的光互连平台,适用于以太网和 InfiniBand 技术。首先,该公司计划在 2026 年初推出 Quantum-X InfiniBand 交换机。每台交换机将提供 115 Tb/s 的吞吐量,支持 144 个端口,每个端口的速率为 800 Gb/s。该系统还集成了 ASIC,具有 14.4 TFLOPS 的网络内处理能力,并支持 Nvidia 的第四代可扩展分层聚合缩减协议 (SHARP),以降低集体操作的延迟。这些交换机将采用液冷散热。

与此同时,Nvidia 计划于 2026 年下半年通过其 Spectrum-X Photonics 平台将 CPO 引入以太网。该平台将基于 Spectrum-6 ASIC,为两款设备供电:SN6810 提供 102.4 Tb/s 带宽,拥有 128 个 800 Gb/s 端口;SN6800 则可扩展至 409.6 Tb/s,拥有 512 个 800 Gb/s 端口。两款设备也都采用液冷技术。

Nvidia 预计其基于 CPO 的交换机将为日益庞大、日益复杂的生成式 AI 应用提供新的 AI 集群支持。由于使用 CPO,此类集群将减少数千个分立组件,从而实现更快的安装速度、更便捷的维护,并降低每个连接的功耗。因此,使用 Quantum-X InfiniBand 和 Spectrum-X Photonics 的集群在启动时间、首次令牌时间和长期可靠性等指标方面均有显著提升。

Nvidia 强调,共封装光学器件并非可选增强功能,而是未来 AI 数据中心的结构性要求。这意味着该公司将把其光互连技术定位为超越 AMD 等竞争对手的机架级 AI 解决方案的关键优势之一。当然,这也是AMD 收购 Enosemi 的原因。

未来之路

关于Nvidia的硅光子计划,需要注意的一点是,其发展与台积电COUPE(紧凑型通用光子引擎)平台的发展紧密契合。后者预计将在未来几年内不断发展,从而提升Nvidia的CPO平台。台积电第一代COUPE采用该公司的SoIC-X封装技术,将65纳米电子集成电路(EIC)与光子集成电路(PIC)堆叠在一起。台积电声称,其 SoIC-X 互连具有极低的阻抗,这意味着 COUPE 在功耗方面非常高效。

关于Nvidia的硅光子计划,需要注意的一点是,其发展与台积电COUPE(紧凑型通用光子引擎)平台的发展紧密契合。后者预计将在未来几年内不断发展,从而提升Nvidia的CPO平台。台积电第一代COUPE采用该公司的SoIC-X封装技术,将65纳米电子集成电路(EIC)与光子集成电路(PIC)堆叠在一起。台积电声称,其 SoIC-X 互连具有极低的阻抗,这意味着 COUPE 在功耗方面非常高效。

COUPE 的发展轨迹主要分为三个阶段。台积电的首款硅光产品是一款用于 OSFP(八进制小型可插拔连接器)的光学引擎,其数据传输速率高达 1.6 Tbps,是目前顶级铜缆以太网解决方案最高速率的两倍。这一初始版本不仅承诺提供卓越的带宽,还提升了能效,解决了现代数据中心的两个关键问题。后续几代 COUPE 旨在进一步突破极限。

第二代硅光产品将 COUPE 集成到 CoWoS 封装(硅基晶圆芯片封装)中,并将光学器件与交换机集成封装。这将实现高达 6.4 Tbps 的主板级光互连。

第三代产品的目标传输速率高达 12.8 Tbps,旨在集成到处理器封装中。该版本仍处于探索阶段,尚未确定发布时间表。台积电表示,正在考虑进一步降低功耗和延迟。

来源:Internet