您当前的位置:检测资讯 > 科研开发

嘉峪检测网 2025-08-24 12:53

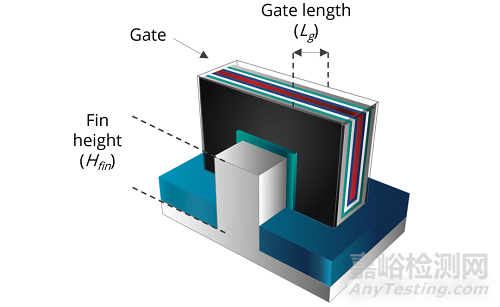

与体硅 CMOS 相比,FinFET 器件在抑制短沟道效应、降低能耗、提升电源电压可扩展性以及提高导通/关断电流比方面均表现更优。

FinFET LDR

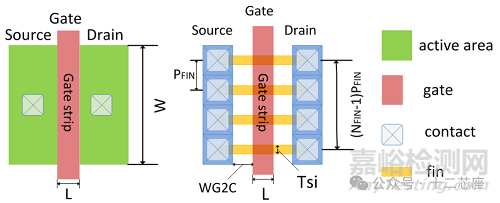

FinFET 的版图密度往往因制造“鳍”所用具体工艺而异,因此难以给出普适结论。Fig1. 对比了传统 CMOS 器件与具有四鳍的短接栅 FinFET 的版图结构:FinFET 采用一条连续的栅极条带,并通过金属连线将多鳍的源、漏端并联,从而构成更宽的有效沟道,这与 CMOS 器件的布局方式截然不同。

LDR: Layout Design Rules

Fig1. CMOS & FinFET LDR

这里采用 λ 基准版图设计规则,对 7 nm FinFET 逻辑单元逐一进行版图刻画。需要指出的是,CMOS 与 FinFET 的版图规则大体一致,差异主要集中在鳍片的制造环节。

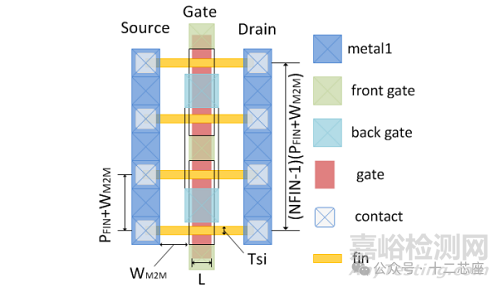

Fig1. 所示的鳍间距 P_FIN 是 FinFET 版图设计的核心几何参数之一,定义为两条相邻平行鳍中心线之间的最小距离,其具体取值由所选 FinFET 工艺决定。业界目前存在两种主流工艺:

光刻定义(lithography-defined):受限于光刻分辨率,P_FIN 较大;

隔离栅定义(spacer-defined):通过更复杂、更昂贵的多重图形化工艺,将 P_FIN 压缩一半,从而获得更高密度 。

本文采用隔离栅定义工艺进行版图参数.

7nm FinFET SG STC Layout

SG STC: Shorted-Gate Standard CellLayout

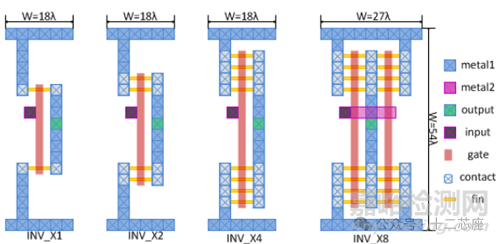

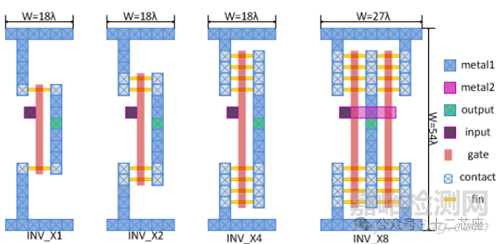

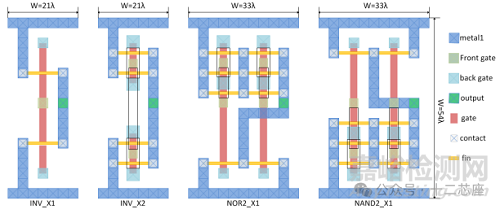

下面展示了若干基本单元的版图示例。本标准单元库中,所有栅极单元统一高 54λ。

INV-1X/2X/4X/8X Layout:

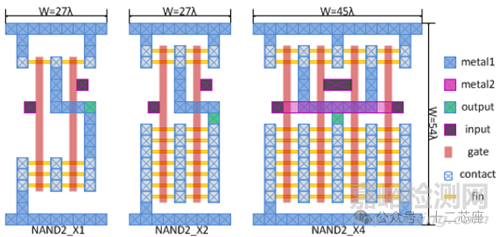

NAND2-1X/2X/4X Layout:

NOR2-1X/2X/4X Layout:

INV-1X/2X/4X 的“有效宽度”均为 18λ;2 输入 NAND-1X/2X 亦为 27λ。INV-8X 与 2 输入 NAND-4X 通过共享扩散与宽度延伸分别达到 27λ 与 45λ 有效宽度;2 输入 NOR 与对应尺寸 NAND 面积相同。其中设计更大单元时,可采用共享源漏区与横向延伸技术。

7nm FinFET IG STC Layout

IG STC: Independent-Gate StandardCell Layout

独立栅(IG)FinFET 的引入带来了一系列新的版图设计规则。栅极被一分为二后,每一段都必须单独引出接触孔,因此需要在每对鳍之间的栅极多晶硅上各放置一个通孔。制约 IG 版图的关键规则是 “CA over PC to RX” :该规则要求在两鳍之间额外预留宽度为 WM2M 的间距,以确保每个栅段都能布设接触孔,如下图所示。

Fig2.具有四个Fin的独立栅极FinFET器件的布局

独立栅(IG)标准单元的版图示例见Fig3. 为保持 SG 与 IG 两种模式间的单元级兼容,所有 IG 单元均沿用 SG 单元的固定高度。

Fig3. 7nm FinFET independent-gate layout of inverters,2-input NAND gates and 2-input NOR gates

Conclusion

纳米级 FinFET 器件凭借卓越的电压可扩展性与设计灵活性,正逐步成为晶体管工艺的首选。本文在 7 nm 节点下,针对短接栅(SG)与独立栅(IG)两种标准单元,系统评估了其在高性能与低功耗场景中的功率密度表现。构建了一套遵循 λ 基准版图规则的 Liberty 格式标准单元库,并对各单元版图进行精确刻画。

来源:十二芯座