您当前的位置:检测资讯 > 科研开发

嘉峪检测网 2022-07-21 12:54

自然界中充斥着静电。对于集成电路行业,每一颗芯片从最开始的生产制造过程、封装过程、测试过程、运输过程到最终的元器件的焊接、组装、使用过程,几乎时刻都伴随着静电,在任何一个环节静电都有可能对芯片造成损伤。

一、半导体的ESD失效特征

ESD对半导体元器件的损伤有以下特征。

(1) 隐蔽性

人体对静电不易觉察,除非发生静电放电,但是发生静电放电时人体也不一定会有电击的感觉,这是因为人体感知的静电放电电压为2~3KV, 而敏感的元器件仅须不到20V的静电放电便能被损坏。对半导体器件而言,人体往往是最大的ESD来源。

(2) 潜在性

有些元器件受到静电损伤后的功能及性能没有明显下降,但造成了潜在的“内伤”。如果元器件完全损坏,必然能在生产及品控中被察觉而排除,影响较小。但如果元器件轻微受伤,在正常测试下不易发现,即使通过老炼也难以暴露问题,基本能蒙混过关,“合格”出厂,直到使用一段时间后(远低于正常寿命,通常在1周~6个月左右),才发现完全损坏。

(3) 随机性

一个元器件自生产开始,一直到它损坏以前,所有的过程都可能受到来自人体、设备、外界环境等静电的威胁,而静电的产生具有随机性,元器件受静电损伤也具有随机性。

(4) 复杂性

在对因静电放电损伤的元器件进行失效分析时,因电子产品的精、细、微小的结构特点而费时、费事、费钱,要求较高的技术,且往往需要使用扫描电镜等高精密贵重仪器。即使如此,有些静电损伤现象也难以与其他原因造成的损伤加以区别,使人误把静电损伤失效当作其他失效。这在对静电放电损害未充分认识之前,常常归因于早期失效或情况不明失效,从而掩盖了失效的真正原因。不但检查不易,而且要耗费多少的人力、财力、时间才能清查出所有环节中的可能存在的影响因素更是难以预计。如果在使用时才察觉故障,其损失将可能是巨大的。

二、半导体工艺对ESD防护能力的影响

随着集成电路工艺不断发展,半导体芯片的速度越来越快,性能也越来越高。在摩尔定律的驱动下,每18个月集成电路的集成度就要翻一番,晶体管的特征尺寸也越来越小,随着晶体管的尺寸进一步缩小,晶体管的尺寸几乎达到了物理极限,单凭减小晶体管的尺寸已经远远不能够使集成电路的发展满足摩尔定律,因此各种先进的工艺制程逐渐被人们所发明。然而,更先进的工艺制程,对集成电路ESD防护能力的影响基本上都是负面的。首先,晶体管的特征尺寸缩小的同时其栅氧化层的厚度也越来越小,从而降低了击穿电压,到了65nm~90nm工艺节点,其栅氧化层厚度更是小于2nm,这将对芯片 ESD保护电路又提出了更加苛刻的要求。表1. 是先进的工艺制程对集成电路芯片的ESD防护能力所带来的影响,结深变浅、轻掺杂漏(LDD)、 外延层(EPI) 、硅化物注入、浅槽隔离(STI)等等这些先进的工艺制程都会降低其ESD防护能力。如LDD结构,其导电沟道两端是非常浅的轻掺杂区域,像两个针尖一样,这种结构下很容易发生尖端放电,从而使得相对于同样尺寸的普通MOS,采用LDD结构的MOS更容易被静电击穿,大大降低其ESD防护能力,即使用很大的尺寸,也很难得到高的ESD防护等级,这种结构的防护等级一般低于1000V。再如金属硅化物(Silicide) 工艺,它的作用是降低MOS晶体管的源漏极串联电阻,使晶体管的工作速度大幅提高,但是当ESD事件发生,并且Silicide 工艺的器件接在芯片电路的输出级时,ESD电流就很容易从芯片PAD传到器件内部,使器件损坏。

表1. 先进工艺制程对ESD防护能力带来的影响

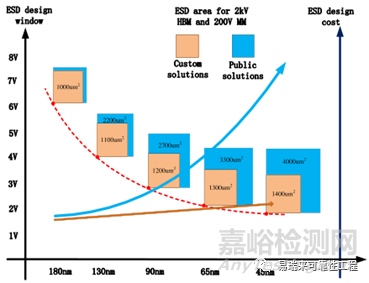

然而这些先进工艺对ESD防护能力的削弱的同时,对于芯片ESD的防护要求不但没有降低,反而要求越来越高,这就要求人们创造出更优的ESD防护电路及方法,当然这也会增加芯片的设计成本。下图1. 显示了Sarnoff Europe公司给出的ESD防护设计成本与ESD设计窗口随着工艺节点减小的变化趋势。

随着集成电路工艺节点逐渐变小,ESD防护的设计窗口也越来越小,即ESD防护越来越困难,并且随着器件尺寸的越来越小,ESD防护的设计成本也迅速增高。从图1.还可以看出,0.18um工艺节点下,通用的ESD解决方案就能达到防护要求,基本不需要专门定制的ESD防护解决方案;而随着工艺节点的缩小,通用的ESD防护方案已经满足不了防护的要求,专用的定制ESD防护方案所占的比例越来越大,从而迅速拉高了ESD防护设计所需的成本。

随着工艺节点的缩小,ESD设计窗口也越来越小,那么限制ESD设计窗口的因素都有哪些呢? ESD防护电路设计的基本原则:

①保护器件在电路正常工作的时候必须处于关闭状态(即没有ESD事件发生时),这与ESD器件的触发电压有关,否则误触发会导致核心电路出现故障;

②当半导体芯片遭遇ESD事件时,该保护器件必须迅速打开(纳秒级别),特别是对于快的ESD事件尤为重要,如器件充电模型(CDM),否则如果保护电路不能及时开启,会导致核心电路损毁;

③芯片pin管脚上的电压(即落在ESD保护器件上的电压与金属互连线上的电压之和),必须不能超过核心电路所能承受的最高电压,否则会导致核心电路损毁;

④在设计的ESD保护等级下,保护电路必须不被损毁,这是ESD器件鲁棒性(robust)相关问题;

⑤在ESD事件发生过后保护器件必须回到关闭状态,否则,器件会进入到被禁止的闩锁状态,导致核心电路发生故障。

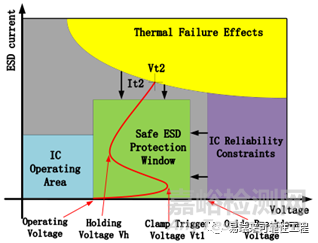

根据上述ESD防护电路的基本设计原则,就可以确定ESD防护电路的设计窗口。首先,对于一个ESD保护电路,其开启电压要低于设计窗口的上限,而窗口的上限是由内部器件栅氧化层的击穿电压决定的,即防护电路的开启电压必须小于栅氧化层击穿电压:其次,对于一个ESD保护电路,其保持电压要高于设计窗口的下限,ESD设计窗口的下限是由电路的正常工作电压决定的,即保持电压要高于电路的正常工作电压,否则,当芯片正常工作的时候,由于未知的原因一旦导致了ESD电路的误开启,防护电路会一直工作下去,直至芯片烧毁;最后,ESD 防护电路工作时,流过其的电流要小于器件的热失效电流,防止二次击穿的发生。下图2.展示了安全的ESD保护窗口的范围。

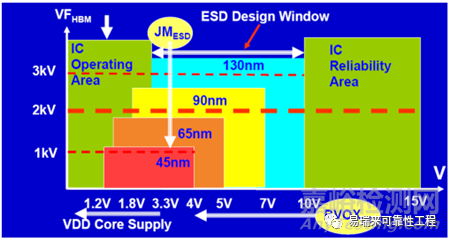

下图3.显示了主流的工艺节点对应的ESD设计窗口,从图中可以明显看出,随着IC设计中的工艺节点的缩小,ESD设计窗口越来越窄,并且抗击ESD电压的能力就越弱。

来源:易瑞来可靠性工程