您当前的位置:检测资讯 > 科研开发

嘉峪检测网 2021-08-31 23:58

芯片是LED最关键的原物料,其质量的好坏,直接决定了LED的性能。特别是用于汽车或固态照明设备的高端LED,绝对不容许出现缺陷,也就是说此类设备的可靠性必须非常高。然而,LED封装厂由于缺乏芯片来料检验的经验和设备,通常不对芯片进行来料检验,在购得不合格的芯片后,往往只能吃哑巴亏。LED芯片来料检验的业务通过运用高端分析仪器鉴定芯片的优劣情况。这一检测服务能够作为LED封装厂/芯片代理厂来料检验的补充,防止不良品芯片入库,避免因芯片质量问题造成灯珠的整体损失。

检测项目:

一、芯片各项性能参数测试

Wd(主波长)、Iv(亮度)、Vf(顺向电压)、Ir(漏电)、ESD(抗静电能力)等芯片的光电性能测试,鉴定供应商提供的产品数据是否达标。

二、芯片缺陷查找

检测内容:

1. 芯片尺寸测量,芯片尺寸及电极大小是否符合要求,电极图案是否完整。

2. 芯片是否存在焊点污染、焊点破损、晶粒破损、晶粒切割大小不

一、晶粒切割倾斜等缺陷。

LED芯片的受损会直接导致LED失效,因此提高LED芯片的可靠性至关重要。蒸镀过程中有时需用弹簧夹固定芯片,因此会产生夹痕。黄光作业若显影不完全及光罩有破洞会使发光区有残余多出的金属。晶粒在前段制程中,各项制程如清洗、蒸镀、黄光、化学蚀刻、熔合、研磨等作业都必须使用镊子及花篮、载具等,因此会有晶粒电极刮伤的情况发生。

芯片电极对焊点的影响:芯片电极本身蒸镀不牢靠,导致焊线后电极脱落或损伤;芯片电极本身可焊性差,会导致焊球虚焊;芯片存储不当会导致电极表面氧化,表面玷污等等,键合表面的轻微污染都可能影响两者间的金属原子扩散,造成失效或虚焊。

3. 芯片外延区的缺陷查找

LED外延片在高温长晶过程中,衬底、MOCVD反应腔内残留的沉积物、外围气体和Mo源都会引入杂质,这些杂质会渗入磊晶层,阻止氮化镓晶体成核,形成各种各样的外延缺陷,最终在外延层表面形成微小坑洞,这些也会严重影响外延片薄膜材料的晶体质量和性能。快速鉴定芯片外延区缺陷的检测方法能够低成本、快速地检测出芯片外延层80%的外延缺陷,帮助LED客户选择高质量的外延片、芯片。

4. 芯片工艺和清洁度观察

电极加工是制作LED芯片的关键工序,包括清洗、蒸镀、黄光、化学蚀刻、熔合、研磨,会接触到很多化学清洗剂,如果芯片清洗不够干净,会使有害化学物残余。这些有害化学物会在LED通电时,与电极发生电化学反应,导致死灯、光衰、暗亮、发黑等现象出现。因此,鉴定芯片化学物残留对LED封装厂来说至关重要。

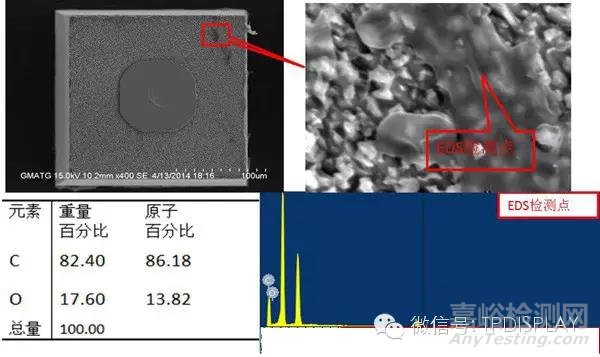

案例分析(一):

某客户红光灯珠发现暗亮问题,但一直找不出原因,委托查找分析失效的原因。经过一系列仪器分析排除封装原因后,对供应商提供的裸晶进行检测,发现每一个芯片的发光区域均有面积不等的污染物,能谱分析结果显示该污染物包含C、O两种元素,表明污染物为有机物。我们建议客户注重对芯片厂商的生产工艺规范和车间环境的考核,并加强对芯片的来料检验。

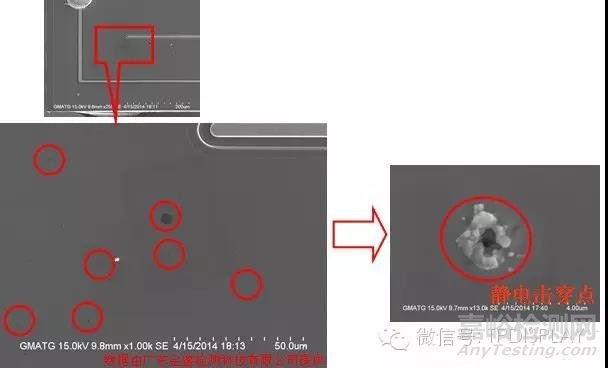

案例分析(二):

某客户生产的一批灯珠出现漏电问题,委托查找原因。通过扫描电镜鉴定这批灯珠漏电原因为静电击穿,并对供应商提供的裸晶进行检测,发现芯片外延层表面有大量黑色空洞,这些缺陷表明外延层晶体质量较差,PN结内部存在缺陷。空洞的发现,帮助客户明确责任事故的负责方,替客户挽回损失。

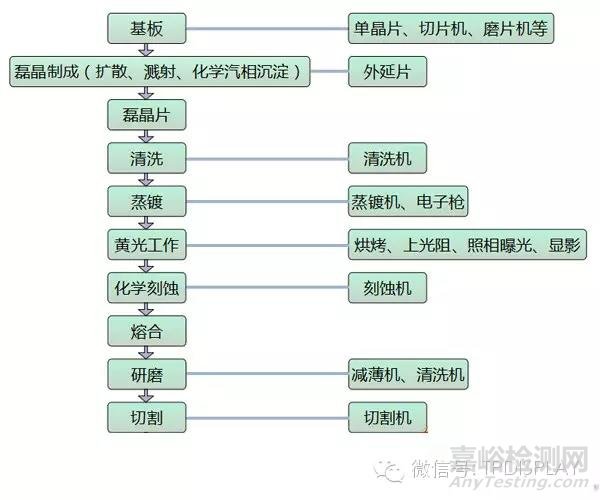

注:LED芯片的制造工艺流程

LED芯片的制造工艺流程图

外延片→清洗→镀透明电极层→透明电极图形光刻→腐蚀→去胶→平台图形光刻→干法刻蚀→去胶→退火→SiO2沉积→窗口图形光刻→SiO2腐蚀→去胶→N极图形光刻→预清洗→镀膜→剥离→退火→P极图形光刻→镀膜→剥离→研磨→切割→芯片→成品测试。

在生长成外延片后,下一步就开始对LED外延片做电极(P极,N极),接着就开始用激光机或钻石刀切割LED外延片,制造成芯片后,然后在晶圆上的不同位置抽取九个点做参数测试。这主要是对电压、波长、亮度进行测试,符合正常出货标准参数的晶圆片继续下一步的操作,不符合要求的,就放在一边另行处理。晶圆切割成芯片后,需要100%的目检(VI/VC),操作者要在放大30倍数的显微镜下进行目测。接着使用全自动分类机根据不同的电压、波长、亮度的预测参数对芯片进行全自动化挑选、测试和分类。最后对LED芯片进行检查(VC)和贴标签。芯片类型、批号、数量和光电测量统计数据记录在标签上,附在蜡光纸的背面。蓝膜上的芯片将做最后的目检测试,目检标准与第一次相同,确保芯片排列整齐和质量合格。

这就是LED芯片的制造流程。下面看一下电路设计如何保护芯片。

静电放电是CMOS电路中最为严重的失效机理之一,严重的会造成电路自我烧毁。本文论述了CMOS集成电路ESD保护的必要性,研究了在CMOS电路中ESD保护结构的设计原理,分析了该结构对版图的相关要求,重点讨论了在I/O电路中ESD保护结构的设计要求。

1、引言

静电放电会给电子器件带来破坏性的后果,它是造成集成电路失效的主要原因之一。随着集成电路工艺不断发展,CMOS电路的特征尺寸不断缩小,管子的栅氧厚度越来越薄,芯片的面积规模越来越大,MOS管能承受的电流和电压也越来越小,而外围的使用环境并未改变,因此要进一步优化电路的抗ESD性能,如何使全芯片有效面积尽可能小、ESD性能可靠性满足要求且不需要增加额外的工艺步骤成为IC设计者主要考虑的问题。

2、ESD保护原理

ESD保护电路的设计目的就是要避免工作电路成为ESD的放电通路而遭到损害,保证在任意两芯片引脚之间发生的ESD,都有适合的低阻旁路将ESD电流引入电源线。这个低阻旁路不但要能吸收ESD电流,还要能箝位工作电路的电压,防止工作电路由于电压过载而受损。在电路正常工作时,抗静电结构是不工作的,这使ESD保护电路还需要有很好的工作稳定性,能在ESD发生时快速响应,在保护电路的同时,抗静电结构自身不能被损坏,抗静电结构的负作用(例如输入延迟)必须在可以接受的范围内,并防止抗静电结构发生闩锁。

3、CMOS电路ESD保护结构的设计

大部分的ESD电流来自电路外部,因此ESD保护电路一般设计在PAD旁,I/O电路内部。典型的I/O电路由输出驱动和输入接收器两部分组成。ESD通过PAD导入芯片内部,因此I/O里所有与PAD直接相连的器件都需要建立与之平行的ESD低阻旁路,将ESD电流引入电压线,再由电压线分布到芯片各个管脚,降低ESD的影响。具体到I/O电路,就是与PAD相连的输出驱动和输入接收器,必须保证在ESD发生时,形成与保护电路并行的低阻通路,旁路ESD电流,且能立即有效地箝位保护电路电压。而在这两部分正常工作时,不影响电路的正常工作。

常用的ESD保护器件有电阻、二极管、双极性晶体管、MOS管、可控硅等。由于MOS管与CMOS工艺兼容性好,因此常采用MOS管构造保护电路。

CMOS工艺条件下的NMOS管有一个横向寄生n-p-n(源极-p型衬底-漏极)晶体管,这个寄生的晶体管开启时能吸收大量的电流。利用这一现象可在较小面积内设计出较高ESD耐压值的保护电路,其中最典型的器件结构就是栅极接地NMOS(GGNMOS,GateGroundedNMOS)。

在正常工作情况下,NMOS横向晶体管不会导通。当ESD发生时,漏极和衬底的耗尽区将发生雪崩,并伴随着电子空穴对的产生。一部分产生的空穴被源极吸收,其余的流过衬底。由于衬底电阻Rsub的存在,使衬底电压提高。当衬底和源之间的PN结正偏时,电子就从源发射进入衬底。这些电子在源漏之间电场的作用下,被加速,产生电子、空穴的碰撞电离,从而形成更多的电子空穴对,使流过n-p-n晶体管的电流不断增加,最终使NMOS晶体管发生二次击穿,此时的击穿不再可逆,则NMOS管损坏。

为了进一步降低输出驱动上NMOS在ESD时两端的电压,可在ESD保护器件与GGNMOS之间加一个电阻。这个电阻不能影响工作信号,因此不能太大。画版图时通常采用多晶硅(poly)电阻。

只采用一级ESD保护,在大ESD电流时,电路内部的管子还是有可能被击穿。GGNMOS导通,由于ESD电流很大,衬底和金属连线上的电阻都不能忽略,此时GGNMOS并不能箝位住输入接收端栅电压,因为让输入接收端栅氧化硅层的电压达到击穿电压的是GGNMOS与输入接收端衬底间的IR压降。为避免这种情况,可在输入接收端附近加一个小尺寸GGNMOS进行二级ESD保护,用它来箝位输入接收端栅电压。

在画版图时,必须注意将二级ESD保护电路紧靠输入接收端,以减小输入接收端与二级ESD保护电路之间衬底及其连线的电阻。为了在较小的面积内画出大尺寸的NMOS管子,在版图中常把它画成手指型,画版图时应严格遵循I/OESD的设计规则。

如果PAD仅作为输出,保护电阻和栅短接地的NMOS就不需要了,其输出级大尺寸的PMOS和NMOS器件本身便可充当ESD防护器件来用,一般输出级都有双保护环,这样可以防止发生闩锁。

来源:慧聪LED屏网