您当前的位置:检测资讯 > 科研开发

嘉峪检测网 2022-03-11 23:29

一前言

不论是过去的3C认证,还是近两年的新3C认证,亦或者其它类型的认证,ESD这个项目一直都是众多硬件工程师难以克服的难题。它为什么会这么“难”呢?

理论上来说,静电是单次出现的干扰现象,没有频率这样的一个固定说法,但是按照静电放电时间纳秒(nS)来算(F=1/T),静电是一个频率较高的干扰信号。

二干扰路径

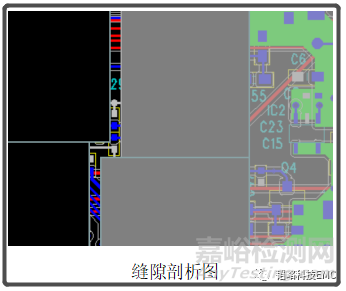

在ESD测试中,一般测试点为外壳的金属部分和缝隙周围,前者(金属部分)是可能存在外壳与PCB的GND存在连接的地方,防止人或者其他带电物体与其接触的时候,发生静电放电对产品形成损坏,后者(缝隙)是因为部分外界干扰可以通过这些缝隙对内部的PCB或者金属部件进行一个静电放电现象。

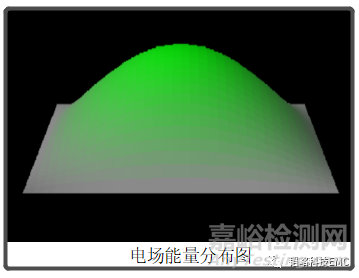

不论是接触放电还是空气放电,对于PCB板来说都可以归于一个“强电场”干扰。只是接触放电的干扰电场会因为距离较远或者PCB走线较长,对PCB内部芯片的干扰能量减弱,而空气放电除了像接触放电一样的原理外,还会因为部分缝隙的原因直接在芯片的上方进行放电,对PCB上的芯片形成“强电场”干扰。

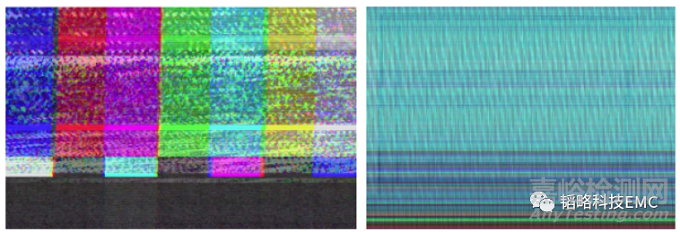

三不重复性

静电问题中比较费解的问题有很多,其中一类就是同一块PCB板在不同的封装外壳下,体现出来的问题各不相同,或者同一批样机在同样的测试条件下,测试结果各不相同,甚至同一台机器在同样的测试条件下,每次测试出来的结果也各不一样!例如下图所示,分别为同一批生产的显示屏分别在8KV接触放电静电测试时测试出来的不同故障状态。

四提前预防

对于静电来说,在研发的阶段是没有办法预测耦合路径和问题点的,所以只能在设计的时候在端口和结构上去做一些预防措施。

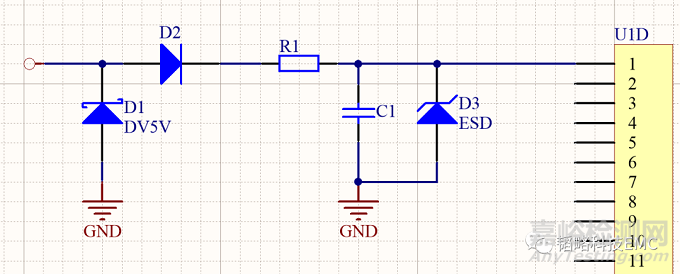

1、端口ESD防护

端口是PCB板必不可少的一个部件,但是它也很容易成为外界干扰进入PCB的一扇“门”,为此很多外接设备的端口都会做成金属的外壳,例如“USB、HDMI、Type-C……”来为静电或者其它干扰做一个引流,将大部分干扰直接引向GND,避免干扰通过信号线束干扰到内部敏感器件。

但是,大多数的情况是金属端口接触放电或者空气放电时,内部金属端子都会受到电场的干扰,从而影响到机器的正常工作。

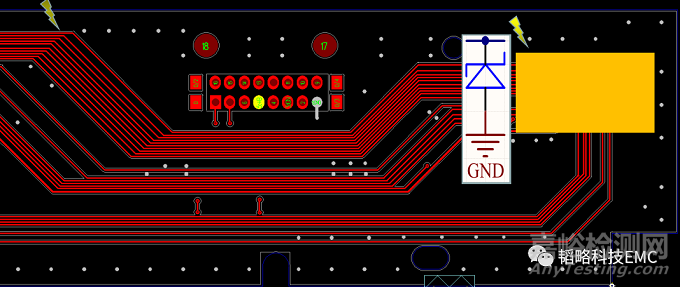

2、多层接地要粗

像电脑的内存条和硬盘这类对信号比较敏感的核心板,很容易被外界的干扰所影响。硬件工程师在设计这类端口的时候,考虑“接地”的问题时,只是从“理想的直流”去看待接地,也就是上下两块PCB板之间有“一根”或者“数根”纤细的pin针连接,在高频的角度来说,这样的接地是“虚假的接地”并不能起到疏导干扰的作用。

高频接地,需要一个比较“粗”的“低阻值”的线路去进行接地,这种的接地方式才会在静电干扰产生的时候,起到一个低阻抗的泄放路径。

3、敏感信号预防

除开上面说的,还需要对一些敏感的信号走线,单独再做二次防护或者多次防护,以确保机器正常工作的时候,不会因为外界的电源波动,信号干扰等因素而导致机器工作异常。

五总结

对于静电问题,需要诸位硬件工程师在前期设计的时候对PCB板上的敏感信号防护、接地路径选择、接地方式选择、端口防护电路的关注不要轻视,因为这些地方都是直接影响机器能否通过静电测试的关键因素。

来源:韬略科技EMC