您当前的位置:检测资讯 > 科研开发

嘉峪检测网 2021-01-20 09:28

我们都知道,随着5G、物联网、汽车等行业的快速发展,这类产品的设计要求也逐步提高,而且更注重应用场景之广、安全性能要求之高。

应用场景之广能达到什么程度呢?上天、立地、入海无处不在。

安全性方面的要求只多不少,尤其是关于电磁干扰的方面,更是重中之重,必须尽量避免发生故障,杜绝麻烦的产生。

有不少电子产品生产上对电磁兼容的印象,还停留在犹如“一纸大学文凭”上,即通过EMC认证就好。然而,如今的电磁兼容设计已经成为系统质量可靠性的重要组成部分。

如果一个产品的系统内部的电磁兼容都无法做好,那么在投入量产之后,这种产品会给社会、商家、个人等造成的影响和后果,有时候完全超出了我们个人的想象。

相信大家都听说过,有些产品在雷雨季节时运行,经常会有大量部件损坏;还有一些产品,在实验调试阶段,每一样指标、性能都完美适配,但到了客户手里却小毛病不断。

这种种的背后,都是产品质量可靠性出了问题。而这些问题当中,有相当一部分都属于电磁兼容性方面,所以,电磁兼容设计已经成为不少企业的一大挑战了。

也正是基于以上的缘由,本文跟大家分享一下电磁兼容设计的内容,打算从两个部分讲解。

第一个部分就是简单的介绍一下电磁兼容性的案例背景。

第二个部分是重点部分,通过两个案例的分享,来延伸出一些电磁兼容的常见理念,且系统地讲解这些理念和理论。因为这些理念和理论可以解决我们平常设计工作中的一些困惑。也是在后续产品设计中需要重点关注的一些要素。

1、案例讲解背景

首先,为何采用案例来讲解呢?

为了帮助大家能够更好地理解和掌握电磁兼容的理念,我们采用了案例的形式。从实际案例来然后上升到理论的分析,这样能让大家更加的感知到理念,理论。以实践的结合,自己对电磁兼容理论的理解也会更加深厚,然后在工作中应用,才能真正的起到作用。这就是“为您所知,只为您所用,为你所有”。

这就是本次课程分享,我个人希望能够帮助大家达到的目标,也是本次交流主题的背景。

2、案例分析

接下来我们着重讲解一下实际操作中的案例。

第一个案例:增大时钟串阻抑制辐射

案例描述:某交换机产品,采用金属外壳,用非屏蔽网线测试,结果出现不满足实验室不确定度4dB要求,故还需要通过优化降低辐射。

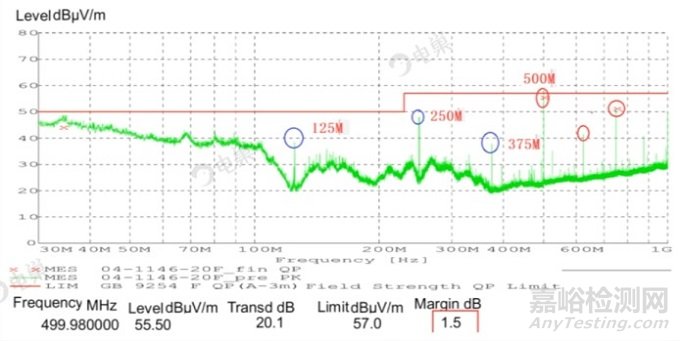

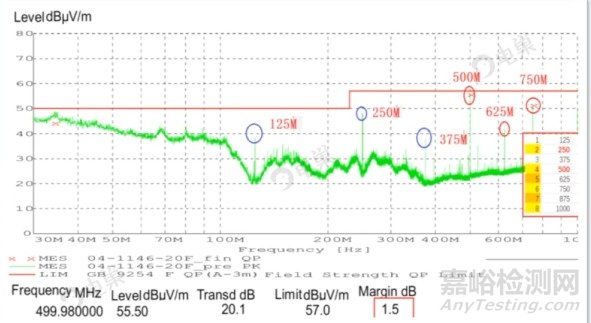

图一

4dB要求的意思就是产品在A实验室通过了测试,假如没有4dB裕量的话,那产品在在B实验室可能就会出现了超标;这其实是与结构设计和信号质量测试都是有个公差裕度的要求是一个道理,所以必须继续进行优化。

问题分析:辐射究竟从哪里来呢?其实我们从图一中可以看到。

如果是有经验的电磁兼容设计工程师或者是测试工程师的,就能够快速发现这个频率点的辐射可能不是从机箱内部的PC版直接辐射出来的,因为这个案例中的交换机采用的是是屏蔽外壳,不是非金属的外壳。

为何说不太可能是从系统内部直接辐射出来呢?

因为图中1G频率点对应的波长,是30公分,那125M对应的是多少呢?那就2.4米。考虑到1/4波长,那就有60公分。60公分的缝隙,在这款交换机上来说,是几乎没有的。所以呢,要想直接从机箱辐射出来了,是比较困难的。

一般而言,30MHz到300MHz,大多数属于电缆带出来的,例如电源线、VGA线缆,USB线等等,当然也不是说高频就没有电缆的问题。电缆如果带了低频,那么高频有些也会带啊,因此需要具体产品具体分析。这是可以作为一个业界经验分享给大家的,希望大家在后续定位的时候能够轻松想到。

问题定位:接下来继续讲一下这个案例定位的过程。

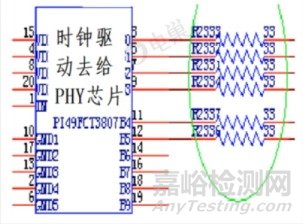

图二

第一步将所有端口的网线去掉,测试的结果是符合要求的。

第二步我们就再回去审查一下原理图,从原理图设计、PCB板设计以及测试PHY芯片的输入时钟信号,并通过采用近场探头进行观察发现,PHY芯片的驱动输入时钟驱动能力够强且辐射很大。

因此考虑在满足PHY输入时钟信号质量的情况下,找开发人员进行沟通与确定,对输入时钟串阻进行调整,从而降低驱动能力。串阻由33欧姆调到51欧姆,抑制辐射获得更好的效果。

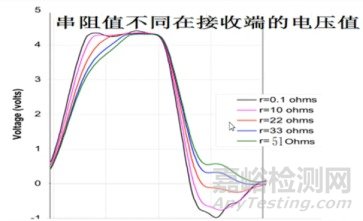

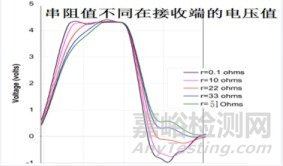

图三

在调整串阻的过程中发现并需要强调的一点是:在图三中,串阻值大小的不同,影响了信号的边沿上升时间,串阻越大边缘越缓。同时,串阻变大,电流也会随之而减小,从而实现辐射能量的降低。

解决措施与结论:

最后,本案例的结论是什么呢?是怎么解决问题的?让我们继续往下看。

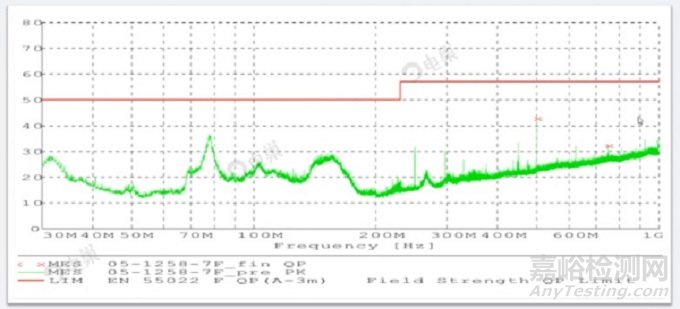

图四

根据前面的图三中我们可以看到,调整这个时钟驱动串阻可以达到降低驱动能力。

由于时钟信号驱动能力强上升沿陡,会产生高次谐波的辐射。在满足信号质量的情况下,可以考虑适当增大时钟驱动器的输出电阻来抑制辐射。

说到这里大家可能也会有疑问,为什么偏偏选择51欧姆。原则上来讲,47欧姆也是可以满足要求的,大家可以在自己遇到这个问题的时候,可以尝试用47欧姆的电阻来试试。

由此我们得出结论是,如果我们选择时钟速率过快,远远超过了系统所需要的,那么电磁兼容的裕量就有可能会因过快的边沿速率而被吃掉,即引发辐射超标。所以呢,在产品开发的过程中,需要关注的是在满足信号质量需求的同时还需要关注EMC设计要求,即综合平衡才是最重要的。

或许有些人想要选择不调串阻、采用屏蔽电缆进行测试,这也不失为一种解决方式,但是在一定程度上会使产品在商用的可应用性受到约束,因为你在实际应用中只能使用屏蔽线而放弃使用非屏蔽线。在这种只能选择屏蔽的情况下,就会降低客户体验。

3、案例延伸理念与理论

从这个案例延伸中,我们还可以延伸一个问题。

图五

图六

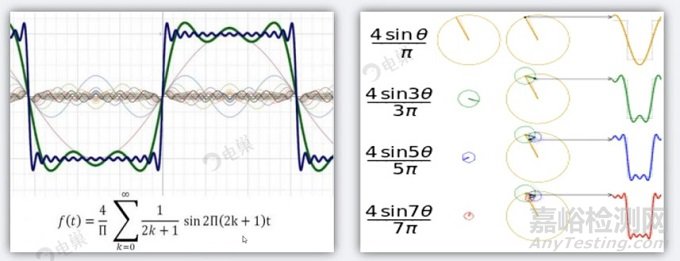

如图五所示,125MHz二次谐波为250MHz,四次谐波为500MHz。而理想方波原理上只有只有基波和奇次谐波, 那么为什么这里会出现偶次谐波呢?

首先,我们一起看看理想的标准方波是怎么构成的?

理想的方波是由正弦波的基波和所有的奇次谐波组合而成,如下图七所示。三次谐波叠加之后的边缘会慢慢变陡,从图七左下方公式也发现结果也一定是奇数。

图七

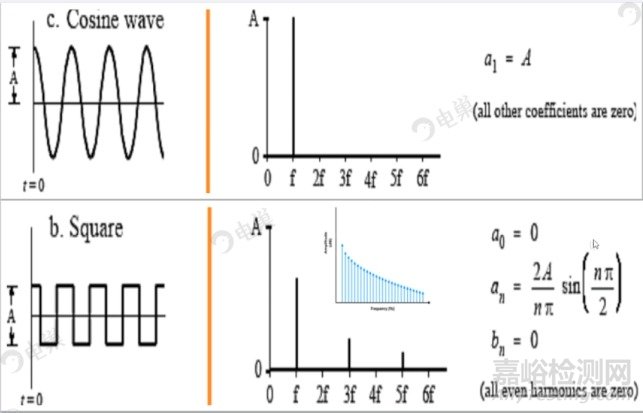

而它们对应的频域又是什么样子的呢?

众所周知,正弦波就是一个频率,在频谱上也只有一根基频。而理想的方波呢?占空比为50%,而且同时上升沿和下降沿也要求相等,我们从下图八的频谱、公式来看,都没有偶次谐波。

图八

那么为什么会出现偶次谐波呢?因为使用了非标准的方波信号,脉冲信号。

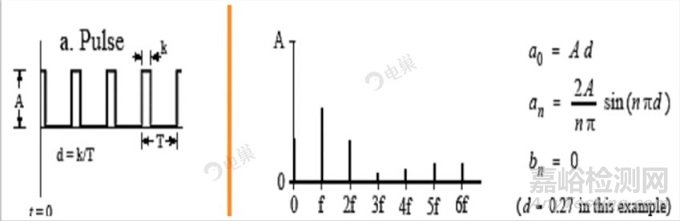

图九

在上图九中可以发现,无论是频谱或者公式都可以计算出偶次谐波,占空比不为50%的脉冲信号就含有偶次谐波。在这里就不再详细展开叙述,只是作为大家在实践过程中的基础知识储备,仅供了解。

来源:电巢EMC