您当前的位置:检测资讯 > 科研开发

嘉峪检测网 2022-02-13 21:38

0、摘要

NASA在低成本集成电路的宇航应用方面持续开展研究。本文针对NASA及其下属各机构在低成本集成电路宇航应用领域的最新成果和方向进行简介,阐述了NASA针对低成本集成电路采取不同策略,并通过标准化研究项目的方式推进,以标准工作形式进行工程推广应用。对我国低成本集成电路宇航应用,以及商业航天元器件发展具有借鉴意义。

1、概述

低成本元器件,尤其是低成本集成电路在宇航领域的应用是国内外研究的热点领域之一。NASA在航天型号项目中注重元器件项目成本与型号项目风险之间的权衡。同时,由于集成电路领域技术发展较快,NASA也注重以尽可能低成本的方式,不断吸纳新的技术,提升系统整体的技术水平先进性。

与高可靠宇航级集成电路相比,尽管低成本集成电路通常在技术先进性方面常具有优势,但NASA在低成本集成电路的应用时仍然趋于保守,并且强调开展标准化项目的研究:一方面考虑不同类型低成本集成电路自身的技术特点,制定针对性的保证策略;另一方面大力推进低成本集成电路宇航应用的标准修订,将经过工程实践检验的低成本集成电路宇航应用技术规范化、流程化,并努力将其融入现有元器件保证体系,以低成本集成电路宇航应用标准作为支点,从而在工程上找到保证航天型号任务成功、控制航天元器件成本、提升航天型号性能先进性之间的平衡点。

NASA在元器件领域的标准研究项目中,NEPAG(NASA Electronic Parts Assurance program,NASA电子元器件保证工作组)为其元器件专业的支撑部门,致力于电子元器件相关标准的编制和维护;元器件用户、标准化组织与元器件供应商协同工作,从而保证NASA、美国国防部以及其他机构所使用的元器件标准的有效性。对于宇航集成电路来说,美国国防后勤局(DLA,Defense Logistics Agency)、NASA喷气动力实验室、美国空军和Aerospace公司等专业机构及公司负责并承担各类质量保证工作。本文在调研上述机构在低成本集成电路宇航应用标准的基础上,简要介绍了NASA在各类型低成本集成电路宇航应用标准化相关方面的关注点以及最新研究进展,为我国低成本集成电路宇航应用的标准化工作提供参考。

2、NASA低成本集成电路宇航应用标准研究的策略

集成电路技术进步非常快,在元器件本身价值相对较高的同时,往往承担电子系统的核心功能。NASA对低成本集成电路的需求并非完全从成本的角度予以考虑,而是更多基于以下原因在宇航型号中选择应用低成本集成电路:

1) 推动新技术的宇航应用,针对性完善标准体系。将先进封装技术引入QML(合格制造商目录,Qualified Manufacturer List)体系,从而获得更高的工作频率、更高功能密度,例如通过引入非密封的大引线数量陶瓷柱栅阵列封装并采用倒装结构的单片SoC产品,规范化低成本元器件的宇航应用。

2) 融合军用及民用标准,结合具体工程需求灵活运用。尤其在宇航型号中,充分考虑体积、重量等方面的需求,综合运用COTS塑封元器件、宇航级器件和军用级元器件的保证手段。将传统的“规避风险”的宇航型号元器件发展模式向“风险管理”模式转变,补齐现有标准体系的短板。

3) 推动低成本元器件宇航应用,全面深入开展低等级标准对标分析。重点针对低等级集成电路,例如汽车级AEC-Q-100、AS 6294/1与美军标之间,开展系统的、全面的标准差异分析,并针对拟应用于宇航领域的低等级元器件开展针对性的评估以及风险控制措施。

3、新质量等级标准发展适应集成电路技术发展趋势

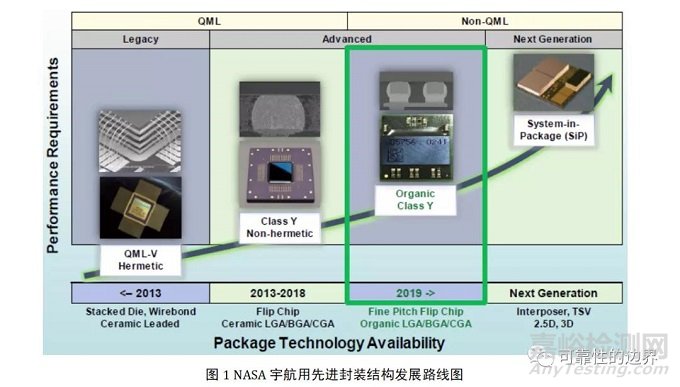

为了在宇航及其他军用元器件标准体系中,加快新技术的融合与应用,NASA喷气动力实验室牵头开展了非密封先进封装器件技术的相关保证技术研究,并提出非密封先进封装器件应采用新的质量等级——Y级,如图1所示。

早在2009年,供应商开始将非密封的TSPC603 32位RISC处理器作为QML Q级产品出售(详细规范SMD 5962-97608)。因此,非密封性已经渗透到QML系统中。根据这一发现, DLA将该产品从QML列表中删除。而就在同时,Xilinx公司大力推动将Viirtex-4(非密封元器件)引入QML系统,作为QML V级元器件进行管理。但是NASA并不赞成此做法。随后提出了一种新的非密封宇航元器件Y级的想法,使Xilinx Virtex-4和其他类似元器件能够在QML覆盖范围内。

2010年初,NEPAG成立了一个新的G-12工作组TG 2010-01,以解决空间用非密封元器件的问题。该团队包括NASA、Aerospace公司、波音公司和DLA的相关专家。

工作组最终选择了Xilinx公司Virtex-4 FPGA作为典型研究对象。前期对此类集成电路进行了辐射和可靠性评估,并引起了空间型号关注,但是由于该系列产品属于非密封封装单片集成电路,迟迟未能按照QML V完成认定。NASA认为这对于航天界和整个QML计划而言是一个重大损失,因为美国宇航型号需要通过供货商控制板图(SCD,Source Control Drawings)进行订购,不利于航天型号任务保证,阻碍了标准化发展,并且其他解决方案价格更加昂贵。在此背景下,NEPAG启动了Y级集成电路标准化方面的努力。

NEPAG工作组在提出了Y级集成电路的概念后,DLA也推动了相应的工程实践项目(EP,Engineering Practice)研究,并启动了MIL-PRF-38535和Y级集成电路详细规范的编制工作。美国Aeroflex公司、Xilinx公司、Honeywell公司、BAE公司、e2v公司等集成电路供应商也积极参与,推动其非密封先进封装集成电路的Y级认定。NEPAG在整合了宇航型号需求、非密封先进封装集成电路主要研制单位优势资源的基础上,开展了涉及参数完整性、倒装芯片BGA与CGA、贱金属电极等相关专项标准化研究项目。

在推进非密封先进封装集成电路的QML Y级标准编制与修订过程中,工作组首先针对V4系列FPGA中使用的用于实现信号完整性的贱金属电极电容器相关的标准,由NASA戈达德空间飞行中心、Aerospace公司、DLA负责,完成了MIL-PRF-32535的修订。而针对JEP163,提出了特殊的筛选、高速信号测试、热点测试等修订要求。而在防静电方面,工作组对于测试和交付过程中的防静电问题予以重点关注。

为了解决非密封先进封装集成电路空间应用过程中设计的新型非传统装配/包装技术独有的可制造性,测试,质量和可靠性问题,NEPAG开展了新技术与美军标的融合以及“包装完整性演示测试计划”(PIDTP)应用方面的工作。通过NEPAG与元器件制造商紧密合作,为制造商提供灵活性,引入了一个名为“包装完整性演示测试计划”(PIDTP)的新概念。每个制造商应制定义一种PIDTP,该PIDTP必须得到空间微电路认证机构(QA)的批准,并在MIL-PRF-38535K中的B.3.11予以体现。NEPAG针对非密封先进封装集成电路空间应用建设的PIDTP要求适用于以下情况:

1) Y级集成电路的非密封结构。参考:MIL-PRF-38535K,H.3.4.4.1.1。

2) 倒装芯片组件。参考:MIL-PRF-38535K,H.3.4.4.1.2。

3) 焊接引线。参考:MIL-PRF-38535K,H.3.4.4.1.3。

4) 电路的元件。参考:MIL-PRF-38535K,H.3.4.4.1。

截至2019年底,典型的Y级非密封先进封装集成电路在宇航QML系统中已经取得了一定进展,首次发布了关于Y级产品的SMD详细规范。NASA对于Y级产品供应商Honeywell、e2v公司已经通过合格认定;Cobham和Xilinx公司正在进行Y级认定;而Cypress公司也已经纳入Y级供应商认定计划中了。

对于已经完成了Y级认定资格的供应商正在积极编制对应的详细规范。其中,Honeywell公司完成单片数字集成电路SMD 5962-17B01《采用倒装芯片及非密封陶瓷外壳结构的HX5000型CMOS SOI工艺抗辐射加固可编程门阵列》的详细规范编制。Cobham公司正在进行单片数字集成电路SMD 5962-17B02《基于90nm标准单元的抗辐射加固数字集成电路》标准的编制。e2V公司正在进行SMD 5962-19205《高性能处理器PC8548》的详细规范的编制。

未来,NASA将针对倒装芯片,底部填充,列网格阵列等的要求,对MIL-PRF-38535进行更多的修订。JEDEC(联合电子设备工程委员会,Joint Electron Device Engineering Council)已经创建了一个有关Y级有机基质的新任务组JC-13.7,推进宇航用Y级集成电路相关标准的征集与编制工作。DLA也将针对Y级产品进行更多工程实践研究。

4、低等级光电器件的宇航应用标准化策略

由于尚未出现用于宇航应用的光电器件鉴定和筛选的标准指南,NASA的应对策略是通过综合运用民用和军用的其他产品标准,由喷气动力实验室负责研究并开发用于鉴定和筛选光电子器件的流程。

在航天型号研制过程中,NASA对于光电无源元件和光电器件均采购低等级COTS产品,因此喷气动力实验室在光电器件的标准发展关注在质量保证方法方面,采取的主要策略是将美军标与电信行业网络设备构建系统标准Telcordia中关于筛选与批次质量保证的工作相融合,形成了适合宇航应用的光电器件的可靠性保证流程指南。

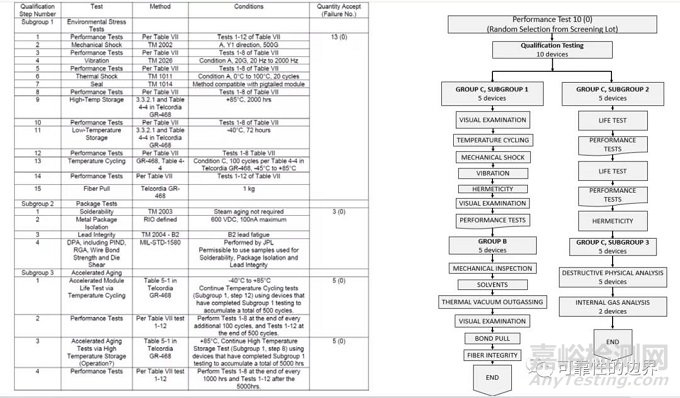

以窄线宽的1.5μm外部光栅半导体有源激光器为例,喷气动力实验室选用了经过筛选和批次质量保证的COTS激光器,使用美军标和Telcordia开发了认证流程,如图2所示。与传统集成电路保证要求相比,喷气动力实验室对激光器的抽样数量进行了减少,试验项目及条件也根据Telcordia做了相应的调整,增加了美军标中给出的包括热真空、强化寿命试验等军用器件具有的保证工作项目。

图2 喷气动力实验室融合军用及民用标准制定的光电器件保证要求

可以看出,针对光电器件,NASA在对光电器件的故障模式有充分的了解基础上,在质量保证标准方面采取了军民标准融合的发展模式,以适应空间应用需求。通过采购成熟COTS光电器件,降低研发与采购成本。尽管在宇航应用的光电器件采购量小,对COTS制造商来说吸引力不大,但是通过在每个测试分组采用尽可能少的样品数量,减少每个步骤的表征参数,来达到成本与质量之间的平衡。

未来喷气动力实验室将继续在光电器件可靠性和故障数据方面拟开展更加深入的研究,通过与其他NASA下属研究中心、大学、行业和其他机构建立合作关系,以应对日新月异的光电子器件,由于没有足够时间来获得失效模式造成的完整可靠性和故障数据的问题,以及来自空间环境,真空,密封性,辐射,温度范围等的挑战,同时继续完善评估和空间鉴定光电器件的方法。

5、通用低成本塑封集成电路标准分析与应用

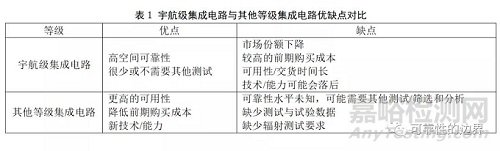

在宇航任务中,集成电路的选择,主要取决于宇航型号风险承受状况、特定任务环境、特定应用程序的约束、进度、可用性和成本等多种因素。在宇航任务中对于元器件的应用,关键是权衡风险与各等级元器件的关系。通常宇航级元器件风险低,但是技术相对落后;其他等级元器件技术先进,但是其风险更高,二者的优缺点见表1。

NASA用于深空探测的立方星、小卫星,出于体积、重量、性能等方面的考虑,常使用通用的低成本塑封集成电路,主要包括符合AEC Q、SAE(美国汽车工程师协会)及其他行业标准的产品,其中不乏有新型号、新任务、新选用的塑封集成电路。其中:

1)在深空探测领域,低成本塑封集成电路最近的成功应用案例是火星立方星一号,该型号由两个功能完全相同的六单元立方体任务伴随Insight火星着陆器。即将开展低成本塑封集成电路深空应用的型号是“火星直升机”,属于“火星2020”火星探测器任务的一部分。它的重量不到4磅,由轻质碳纤维和铝,硅和铝箔等其他材料制成。

2)在立方星领域,由于对低成本通信卫星的需求,以及围绕地球观测服务发展的新业务等,使得低成本塑封集成电路的使用也是日益增长。同时,更加推动了对更小,更轻,成本更低的航天器的新产品解决方案的需求,而这些解决方案无法使用传统的符合宇航标准的1级密封QML / QPL产品进行生产。对于立方星和小卫星而言,由于卫星主要在近地轨道和地球同步轨道中运行相对较短的时间,对于集成电路的耐用性和辐射要求大大降低。对于这样的任务,DLA进行辐射加固的宇航级元器件通常要求过度严格。

在NASA看来,这并不是说对标准QML产品的需求正在消失,而是NASA与主要供应商,例如TI、ADI、Cobham和Renesas等公司,根据低成本塑封集成电路在质量、可靠性、抗辐射能力和成本等方面进行权衡,提供了多种解决方案,在新的宇航型号中基于SAE国际航空航天标准AS6294/1,混合使用抗辐射加固和商业开发的集成电路。

ADI公司提供三种等级的商业航天集成电路产品:CSL,CSM和CSH。在被ADI收购之前,Linear Tech(LTC)已开发出RT(抗辐射)产品系列,而后由CSH取代了RT系列。Linear Tech提供的PEM LTC1604 24位A / D转换器经过筛选,使用NASA开发的流程。

Cobham公司致力于定义产品技术和相关的筛选流程,以优化并适应于星座空间应用。LeanREL方法旨在满足辐射性能、可靠性、可追溯性和成本方面的任务保证要求。如图5所示。

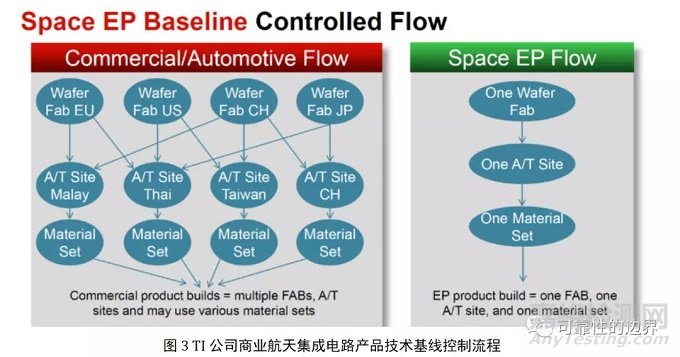

对于塑封集成电路,必须综合考虑体积小,重量轻,性能高和成本低的优点,以及适应宇航型号在元器件可追溯性的流程管理方面所面临的困难。图3所示TI公司商业航天集成电路产品技术基线控制流程说明,商业用或汽车级的COTS集成电路产品可能在多个晶圆厂、注塑厂、组装/测试工厂生产,并且可能使用各种原材料。但是用于宇航型号研制流程的塑封元器件对生产过程进行了固化并使其可追溯。

汽车级EEE元器件在宇航中也有所应用,特别是在小卫星上,主要是基于以下考虑:

1) AEC认证的元器件在汽车应用中(震动,振动,热循环,高温)具有较高的可靠性水平。

2) 宇航级元器件前期购买价格较高,对于强调低成本的运载火箭和小卫星考虑使用其他等级元器件。

3) 在技术先进性方面,COTS元器件发展更快。

4) 由于汽车级集成电路大量为塑封,在体积、重量方面存在优势。

5) 美国航天工业不再能够完全控制集成电路的市场发展。

自从NEPAG成立近20年以来,标准是与时俱进的,始终努力保持与工程约束、新技术和当前的COTS发展同步。NEPAG组织JEDEC标准化工作组JC-14.3与SAE标准工作组CE-12开展了塑封集成电路标准对标流程研究项目,为潜在的NASA应用需求开展低成本塑封集成电路标准对标与评估。

以汽车级集成电路为例,尽管汽车级集成电路种类与功能齐全,符合AEC-Q-100规范要求的汽车级集成电路似乎为小型宇航型号用户提供了技术与采购优势,但毕竟汽车级集成电路是为了满足地面交通工具而研制,NASA对汽车级集成电路的评估仍然非常有限。在质量保证理念方面,AEC-Q-100规范仅是“资格要求”,重点在于:

1) 汽车级集成电路注重“系列”的一次性初始认证;

2) “集成电路系列”根据常用材料、过程、设计、制造地点等进行划分;

3) 如果可以证明数据的相关性,则可以使用“通用数据”;

4) 不同批次之间的测试/保证水平可能有所不同;

5) 筛选可以作为制造商自身要求的一部分,也可以作为制造商与其客户(PPAP)之间的协议来执行,不具有强制性;

6) 对汽车客户的流程变更通知(PCN)的要求。

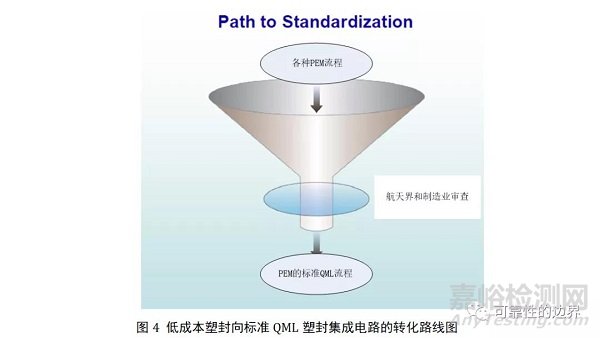

上述“资格要求”并不适用于DLA与NASA对于元器件的QML认证体系。针对这一问题,SAE标准工作组CE-12成立超过65位来自波音,洛克希德,NG,L-3,航空,NASA,Xilinx,ON,TI,ADI,英特尔,陆军,空军,霍尼韦尔,IRF,罗克韦尔·柯林斯,DLA,BAE,Integra Technologies,Hi-Rel Lab的技术专家组成的专家组,制定了低成本塑封集成电路标准与分析的路线(如图4所示)。并以周会议(平均不少于15位专家参会)的形式进行沟通,并解决DLA负责的航天、航空、地面装备使用的低成本塑封集成电路应用评估及保证技术方面的问题。

重点分析各类不同的塑封集成电路,通过宇航界和制造商共同组成的专业委员会审查,形成符合QML标准体系要求的塑封集成电路认定与保证工作流程。从而实现将越来越受到认可的汽车级以及其他正在使用的COTS集成电路,经过筛选和鉴定后用于宇航、航空和地面电子产品。而在上述塑封集成电路认定与保证工作流程中涉及到的试验/测试方法均是以MSFC-STD-3012作为基准,并交叉引用PEM-INST-001,MIL手册和标准,JEDEC相关标准文件。宇航级集成电路与其他等级集成电路的性能通过对相关标准的对比可以看出差异,后者依据的标准较前者均缺少相应的关键测试,MIL-PRF-38535与AEC-Q-100集成电路相比较,AEC-Q100中缺少关键测试。

因此,NASA开展通用低成本塑封集成电路标准分析与应用工作的关键是通过系统的标准对标分析,找到传统MIL-PRF和MIL-STD与其他标准体系(例如AEC)之间的差异,形成标准比较矩阵,再通过针对性地补充过程管理、抗辐射评估、筛选、破坏性物理分析、失效率与寿命试验、失效模式和影响分析等工作,降低其他等级集成电路的宇航应用风险。

6、结论与启示

本文介绍了NASA在低成本元器件宇航应用标准方面的研究进展,可以将美国宇航界在低成本集成电路选用和保证的基本策略概括为“分头负责,区分对待,谨慎跨域,标准落地”。

在分工方面,由NASA下辖各机构以及NEPAG提出低成本集成电路的宇航应用需求,以及保证技术和流程研发的需求;DLA针对NASA的需求予以研究专项立项支持,通过工程实践研究专项的方式逐步推进;以低成本集成电路生产商为主的工业界具体实施相关研究项目,并通过JEDEC等标准转化落地。

在低成本元器件宇航应用相关研究中,NASA根据不同类型的集成电路因地制宜地制定保证策略以及标准化工作,包括制定新的质量等级、标准融合发展、跨领域低等级标准对标与风险控制等多种方式相结合,在基于标准专项基础研究成果基础上,不断完善现有QML体系的同时,促进并保证新技术在宇航领域可靠应用,具有重要借鉴意义。

参考文献

[1] 胡楠楠,南方.低成本批产商业通信卫星用元器件保障模式探索[J].数字通信世界,2018,(8):247,259.

[2] Shri Agarwal. Advanced Packaging Class Y –Non-hermeticsfor Space- Infusion of New Technology into Military Standards[C].NASA NEPP ETW 2019.

[3] Sung Hong,Allyson Yarbrough.Guide to Using Automotive-Grade EEEE Parts in Space Applications[C].NASA Electronics Parts and Packaging (NEPP) Workshop.2018.

[4] Shri Agarwal.PEDs and PEMs in Space Standards Readiness for PEMs[C].NASA NEPP ETW,2019.

[5] Sultan Ali Lilani, Jonathan Hochstetler. AS6294/1 and AS6294/3 – PEMs and PEDs for Space [C]. 2019 NASA NEPP Electronics Technology Working Group Meeting. 2019.

[6] Alireza Azizi. Qualification & Reliability of Photonic Devices System Perspective[C]. NEPP Electronics Technology Workshop. 2019.

[7] AS6294 / 1 Requirments for plastic encapsulated microcircuits in space application[S].

[8] AEC-Q-100 FAILURE MECHANISM BASED STRESS TEST QUALIFICATION FOR INTEGRATED CIRCUITS[S].

[9] MSFC-STD-3012 Electrical, electronic, electromechanical(EEE) parts management and control requirements for MSFC Spaceflight hardware[S]

[10] MIL-PRF-38535K Integrated circuits (microcircuits) manufacturing, general specification for[S]

[11] MIL-PRF-32535 Base-metal electrode(BME) ceramic caps[S]

[12] PEM-INST-001 Instructions for Plastic Encapsulated Microcircuit(PEM) selection, screening, and qualification[S]

[13] JEP163 Selection of burn-in/life test conditions and critical parameters for QML microcircuits

来源:可靠性的边界