您当前的位置:检测资讯 > 科研开发

嘉峪检测网 2022-03-02 23:04

封装工艺是为了提升电子设备运行的可靠性,采取的相应保护措施,即针对可能发生的力学、化学或者环境等不确定因素的攻击,利用封装技术和特殊材料对电子设备进行保护。

封装技术已经广泛应用于航空航天设备、汽车、计算机以及移动通信设备等诸多领域中。但伴随着超低压、超高压、强湿热、大温差等特殊条件下电子设备运行要求的增加,加之封装器件日趋大功率应用、小尺寸化、功能高集成化以及越发复杂化的因素,经常发生因为封装失效引起电子设备运行过程中故障问题,严重影响了功率器件的可靠性。

因此,封装失效问题以及如何对封装工艺进行优化,是目前封装行业需要研究的课题。

1、功率器件的失效分析

1.1焊料空洞导致EOS失效

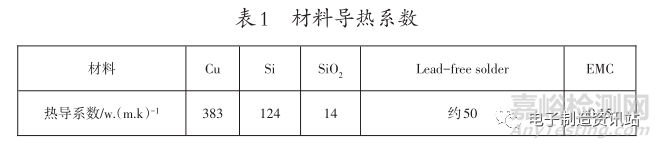

本文借鉴了相关文献的研究成果,确定了影响器件散热的因素为焊料的空洞,对不同尺寸空洞影响器件散热的程度进行深刻分析,并以此为基础深入探讨研究器件芯片可靠性受焊料空洞影响程度及其热应力的状况。表1显示材料的热导系数。

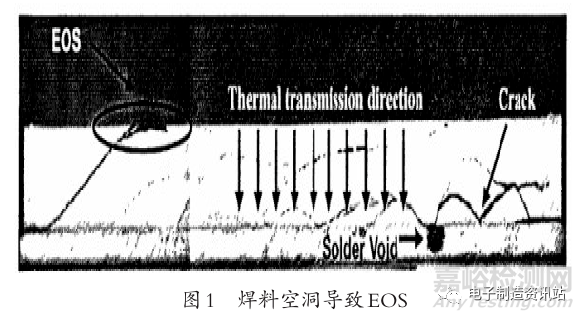

目前广泛应用的环氧塑封料形式呈现热导系数非常低,热导体效果不佳,功率器件运行中形成的热量传递的途径唯有芯片。如图1所示,图1中箭头的方向就是芯片在工作状态下产生热的传输方向。从图1中不难看出,如果焊料内空洞形成的原因是器件生产过程中工艺不当,基于空气导热系数只有0.03w/ (m.k),表现热导体的不佳状态,器件散热受到影响,在这样的状态下长久运行,ESO会因为大量热量的积累而导致器件失效。

1.2栅极开路导致EOS失效

场效应晶体管(mosfet),是电压管控的一种手段,在绝缘层的沟道区对栅压实施有效的管控,而利用栅压大小的改变对此区域的载流子浓度实施调控,从而确保源漏间电流大小的有效控制。因为打线不牢导致栅极引线升离或是因为长时间的热循环让引线根部裂纹产生断裂后,产生栅极开路,从而失去栅极控制电流的能力,引发EOS,导致器件失效。

1.3芯片裂纹导致EOS失效

硬而脆的单晶硅晶体具备金刚石的品质,一旦形成硅片受力容易脆断与开裂。在引线键合、晶圆减薄、芯片焊接、圆片划片等工序中都可以形成硅芯片裂纹。

通常情况下,芯片只是在引线区域外的微裂纹,就难以被发现,最糟糕的情况是在工艺实施中没有发现芯片裂纹,更甚者是电学测试芯片的时候,微裂纹的芯片与没有裂纹的芯片在电特反应上不存在差别,但微裂纹会危及封装后器件的可靠性、降低器件的使用年限。

裂纹只有下列几种情况才能显示出来:采用十分靠谱的高低温循环实验或者是器件散热时候瞬间加热,呈现不匹配的芯片和封装材料热膨胀系数,还有运行中的外界应力作用等。否则是难以发现裂纹的,这也会成为器件封装失效的原因。

2、功率器件封装工艺优化研究

2.1、问题分析

在功率器件封装工艺中,最关键的工序就是芯片焊接。焊接过程是利用熔融合金焊料将芯片与引线框架结合,使引线框架散热器与芯片集热器的欧姆接触形成良好的散热途径。

因为性质不同的粘结剂和固体表面,以及化学、吸附、力学、静电、配位键、扩散等诸多因素,并不能对不同表面和粘结剂粘结的道理做出清楚解释。同时,气体、油污、尘埃等污染物都会被固体表面所吸附,导致表面因为氧化膜而污迹斑斑。

另外,基于加工精度的影响,因为加工精度不够,固体表面会存在宏观和微观的几何形状误差,粘贴的界面只是中几何面积的2%-7%,所以,严重降低了粘结剂对固体表面的保湿功能。所以,针对器件封装的芯片焊接工艺,焊料中的空洞成为最严重的问题,不仅削弱了器件的散热能力、阻碍了与欧姆接触,更对功率器件的可靠性构成威胁。

由于芯片必须先焊接在引线框架上,然后将芯片连接到框架上,最后实施高温焊接,因为器件和粘合剂类型的差异性,也会呈现不同的焊接曲线和温度。

2.2优化措施确定

在优化电源装置的焊接工艺之前,对该装置进行 x 射线扫描。结果表明,焊料空洞约占芯片面积的1%-7% 。按照电源装置的有关规定,焊料里的空洞大小不超过芯片面积的百分之十才可定性为合格产品。

可是在具体的运行实践显示,就算低于10%的空洞面积的器件可靠性也难以保障。本文的试验利用对时间曲线、焊接温度的优化,以减少焊料的空洞,明显提升了器件的可靠性、让使用寿命得以有效延长。

2.3优化效果对比分析

在进行芯片封装工艺优化之前,试验样品选择的片焊温度-时间曲线温度最高值358.9℃,熔融时间为37分钟,焊接后降温速率是9.71℃/秒;工艺实施优化后,芯片焊接温度-时间曲线的最高温度为358.3℃,需要39分熔融时间,焊接后的降温速率为8.95℃/秒。

提升相关工序的温度,可以促进芯片下焊膏的流动性,加速焊膏内空气的排出;而对焊后降温速率的降低,有助于对芯片的保护,最大限度避免芯片产生裂纹。

针对优化措施前、优化措施后,随机分别抽取5个样品,利用X—Ray对焊料的空洞实施测量同时对两者的结果进行比较,结果显示,在工艺优化措施实施前焊料空洞量为1.4%-6.6%之间。

优化前,芯片焊接空洞的孔隙率不同,部分孔隙率甚至达到10% 的最大范围。而对芯片的焊接采用优化措施后的焊接曲线,器件的焊料空洞已经没有,表现显著的优化效果。焊接温度的提高会让热应力加强,但优化结果获悉,焊料的空洞更能够减少。

因为考虑到提升器件的可靠性,虽然极大的应力会因为焊接温度升高而加大,但空洞减少的价值和意义更大。同时测试优化前后的样品采用Undamped Inductive Loading进行测试,Uil 可以作为衡量设备阻力的参数。

测试原理如下: 将栅极电压施加到器件上后,由外部电源对电感器进行充电,直至电感器产生预期的电流测试值,从而完成电感器的充电过程; 电感器对器件进行反向放电,完成电感器的放电过程。

感应器反向放电到设备,会导致器件的雪崩状态,以此测试器件的抗EOS能力。对优化前后的两组样品,随机抽取15个样品进行 uil 检测,测试公式为:V DD =23V,V GS =10V,L=0.3mH。同时,对物态方程的能量和电流进行了比较和分析。

实验结果表明,eos的能量为279.3mj,平均电流为41.8a,没有焊接腔的 eos 的能量为307.6mj,平均电流为46.1a。因此,无焊接腔器件必须具有较高的能量和电流才能导致 eos 失效,因此,没有焊点的器件比有焊点的器件具有更高的抗失效能力。

3、结束语

尽管目前对封装实效问题的研究已经成为热点,也取得了一定成效。但对于封装失效形成以及演化规律的研究才刚刚开始,以往的多数研究主要是基于对封装材料的研究,对金属与聚合物界面的影响关注甚少。

所以,对封装失效问题的后续的深入研究,必须在现有基础上进行关键的补充,研究领域应该注重封装功率器件整体的关注,要以器件与封装材料界面彼此作用前提下,综合试验研究与仿真建模研究的实践数据,对封装失效过程的形成、变化的轨迹以及多场耦合效应进行全面分析,找出功率器件实际使用寿命低于预期使用寿命的真正原因,为提升封装工艺以及器件的可靠性提供帮助。

来源:君芯科技