您当前的位置:检测资讯 > 科研开发

嘉峪检测网 2021-07-30 11:58

可维护性和可靠性验收非常重要,硬件维护工程师在后端发现问题后,总结成可维护性和可靠性需求,在产品立项的时候与新特性一起进行需求分析,然后经过设计、开发和测试环节后,在产品中落地。这些需求最终实现的效果是否和需求提出人想要达到的效果一致,需要硬件维护工程师进行验收。

硬件维护工程师越早参与,效果越好。如果等到转维审查的时候才参与验收,发现偏差需要修改和测试,相当于需求要重新开发一次。推荐硬件维护工程师在需求分解的时候就参与,然后在开发和测试的时候再进行一次审视。

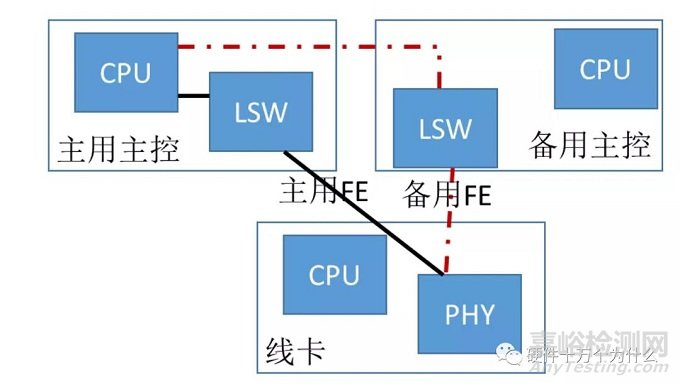

有一个典型的案例,某款主力发货的款型,框架如下,主用主控通过FE通道对线卡进行管理。线卡到主用主控有两条通道:通道1——通过主用FE到主用主控的LSW、然后再到主用主控的CPU,下图中的实线通道;通道2——通过备用FE到备用主控的LSW、然后再到主用主控的CPU,下图中的虚线通道。

当时出现一个特别奇怪的现象,每天到固定的时间点,线卡板就开始复位,复位后线卡板无法注册。进一步定位,发现线卡板到主用主控的FE通道有错包,造成管理报文丢包。由于主用和备用FE通道的切换机制没有做好(可靠性需求实现有偏差),主用主控在切换FE通道之前就认为线卡板发生问题、从而将线卡板复位。线卡板复位后,仍然通过主用FE通道与主用主控协商,FE通道丢包造成协商失败,线卡板无法注册。

顺着错包往下排查,发现错包发生在主用主控的LSW芯片。单板返回实验室测试,发现丢包发生在固定的温度区间。当环境温度在25℃左右时发生丢包,低于20℃或高于30℃都不会丢包。通过交叉芯片进行排查,最后发现丢包是由晶振引起的。在环境温度25℃左右时(晶振表面温度50℃),125M晶振会发生跳频。晶振的规格是125M±10ppm,在在环境温度25℃时,晶振的频偏达到了20ppm,超出规格1倍。

这个问题是一个典型的可靠性问题,有以下几点可以改进:

1)主控的FE通道切换机制改进,当其中一条FE通道故障时,优先进行通道切换。

2)故障定界优化,当主用主控到多个线卡板的FE通道都出现故障时,判断为主用主控故障,优先进行主备倒换,把业务切换到备用主控,而不是复位线卡板。

3)FE通道记录错包日志,错包每增加一定数量,记录一条日志。

4)主控发现线卡异常时,先上报告警。有业务备份通道的,切换业务后再复位线卡;没业务备份通道的,只告警,不复位线卡。

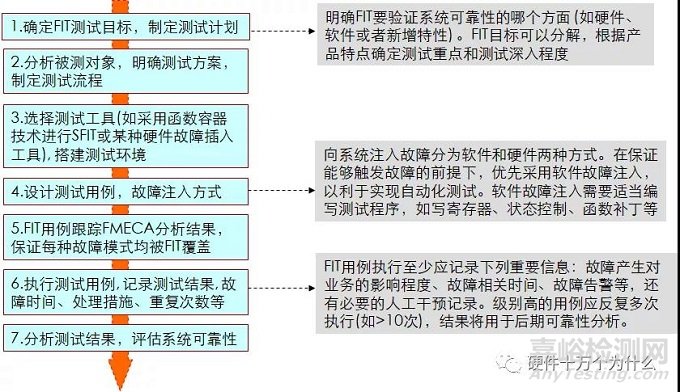

FIT:FaultInjection Test(失效注入试验)

可靠性FIT测试验证目的:

Ø 可靠性增长,测试发现问题,提高系统可靠性;

Ø 验证系统可靠性,验证系统的故障恢复能力、故障管理能力;

Ø 对产品故障恢复能力定量估计(可靠性指标验证);

开发阶段一般不可能验证产品的MTBF,因为:

Ø可靠性是基于统计的结果,需要有足够的样本量

Ø时间较长;试验量大

Ø难以模拟现场应用环境

我们需要FIT测试来验证可靠性,作为可靠性设计的验收

FIT方案设计基于两个原则:

一是保证测试的覆盖率

二是保证测试工作量的可执行性

用例设计中考虑故障出现的概率(根据FMECA分析结果)。对可能产生同一种影响的不同故障考虑故障模式的收敛,即只模拟一种故障模式(前提故障检测是通过检测这些故障模产生的故障影响来确定故障,而不是直接检测故障模式)

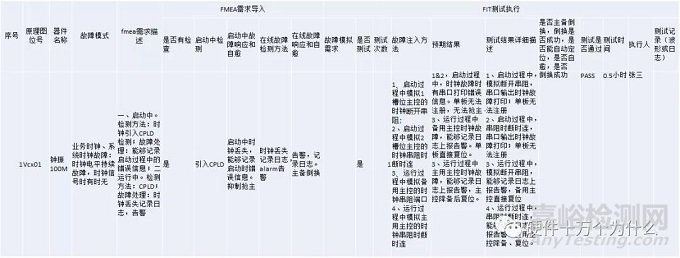

FEMA分析作为可靠性设计的需求,那么我们设计好FIT测试作为验收手段。

表格具体内容可以不关注,掌握相关方法即可。

来源:硬件十万个为什么