您当前的位置:检测资讯 > 科研开发

嘉峪检测网 2023-03-08 08:21

(1)预布局

在总体阶段的时候,我们应该就器件选型、预布局、热设计、结构设计的可行性进行了评估,输出的核心器件选型结论、预布局结论应该是满足总体的热设计和结构设计要求的。

根据初步方案,输出预布局原理图,要求原理图至少包含主要器件、电源、热敏感器件和接插件。硬件工程师要规划好,单板、器件功能和信号流向。

PCB预布局是热设计的重要入口条件。开展热设计仿真,硬件工程师需要给热设计工程师提供单板布局和器件热耗(功耗)表、各器件散热参数。数字器件要注意提供尽量准确的功耗数据,特别是DDR/FPGA等器件要根据使用场景进行计算。

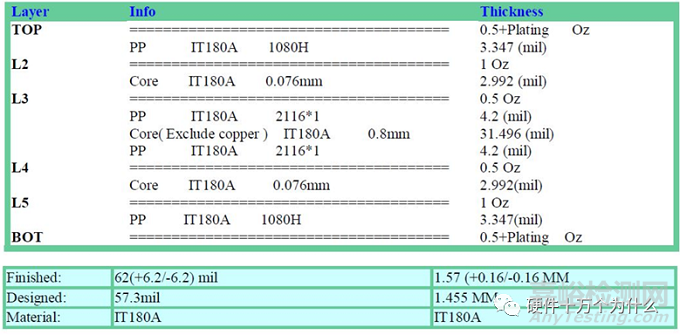

预布局除了完成关键器件的摆放,评估PCB的可行性,还需要确定电路板的层数和层叠结构。按照这些总线的要求,下一步要设计层叠结构以及计算各类总线要求的阻抗和传输线的物理尺寸。下图是项目设计的层叠结构:

从层叠结构上,可以看到本设计需要使用6层板,6层板可以有3个信号层Top层、L3或者L4和BOT层;也可以有4个信号层,Top层、L3、L4和BOT层。具体需要使用几层,根据实际的情况来确定,本设计就使用了4个信号层。PCB板的厚度为1.57mm,使用的材料是IT-180A,其中使用了4张PP和3张Core。

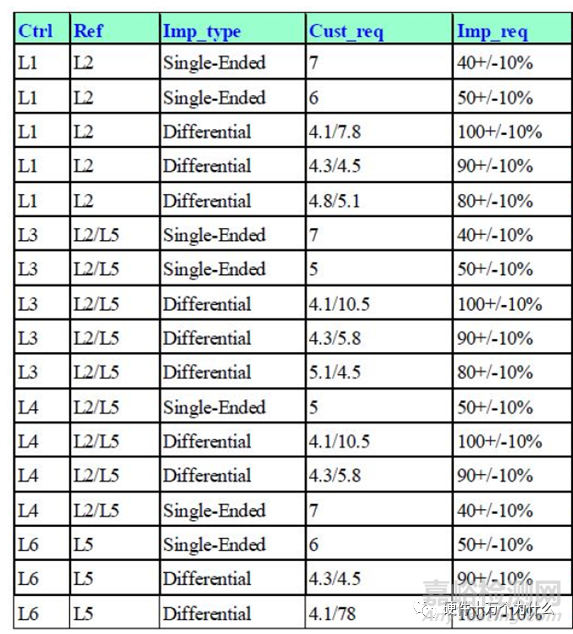

根据层叠结构计算传输线的阻抗,由于有4个布线层,层叠又是对称结构设计的,所以只要计算TOP和L3层的阻抗即可,其它两层都是一一。本设计中的高速总线类型比较多,既有单端的布线,也有差分布线,既有单端40ohm的DDR4布线,也有单端DDR4的50ohm布线,既有差分80ohm的布线,也有差分90ohm和100ohm的布线。结合TOP层和L3层一起,所有的阻抗要求以及布线结构如下图所示:

图 各层布线阻抗计算结果

从计算结果可以看到,看似非常简单的一个高速产品设计,其阻抗就有多达10组设计。在实际的应用中,要仔细区分。

(2)结构设计

结构设计需要包含:

① PCB外形轮廓尺寸

包括结构所需的倒角、凸凹槽、内部开窗等信息。

② PCB板厚度

常用的厚度有1mm、1.6mm、2mm、2.4mm规格。

单独列出来是因为厚度是直接参与到结构设计的叠加累计尺寸当中,需要重视。

③ 外部接口器件的位置和外形

LED的位置;网口、串口;光口;电源开关;电源插座;复位按键;背板连接器;导套、导销;USB。

外形一般在3D设计的时候,就会把接口零件模型组装到PCB,一起投影到DXF文档,同时提供定位参考点。

④ PCB安装孔的位置、孔径及其禁布区要求

选用什么型号的螺丝,提供相应孔径的尺寸,提供螺帽禁布区尺寸,并提供文字说明。所选焊接器件的料号、位置和放置面。

其他需要焊接到PCB上的与结构相关器件的规格型号,位置信息,禁布信息,放置到PCB哪一面等信息。例如焊接螺母、螺柱;较大尺寸的电源砖;较大尺寸的芯片;需要散热的芯片。

⑤ PCB的TOP和BOTTOM面对器件高度的限制要求

由于PCBA需要与结构件装配,所以需要提供允许摆放电子元件的高度要求,需考虑间隙余量。

⑥ 光纤半径和路径要求

光纤有弯曲半径要求,所以盘纤的方式、盘纤的路径和路径的宽度都要提前规划好,这些信息与PCB相互影响。

⑦ 直接安装到PCB表面的零件

有些金属结构件直接安装到PCB表面,表面一般禁布线,并且金属外围轮廓需增大,留足余量,比如零件制造装配公差引起短路。

有些塑胶零件安装到PCB表面,表面一般禁布元件,禁布区外围余量留足。

⑧插板式PCB标示出插槽限高或禁布区域以及行程要求。

有一种插板式PCB,两侧边直接与导轨插槽滑动装配,两边禁布区要求,以及注意模拟行程当中其他结构件会发生撞击干涉的空间,明确限高或者禁布要求。有一种PCB装配方式带滑动行程,注意模拟装配行程当中与结构件会发生撞击干涉的长度和面积,明确限高或者禁布要求。

⑨ 焊接器件引脚长度要求。

⑩ 连接器的PIN序列信息。

⑪散热器安装位置,高度、禁布区要求。

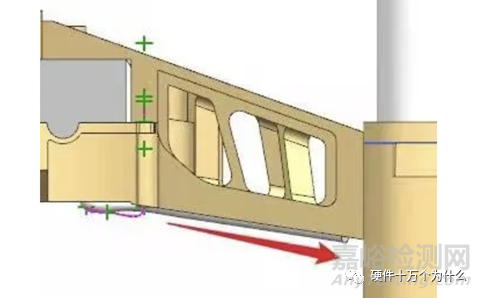

⑫特殊器件的安装要求,例如摄像头、陀螺仪传感器、ToF等器件可能需要有安装位置的特定要求。图是一块电路板在总体设计过程中考虑结构干涉、电路板安装、天线安装的示意图。

电路板安装示意图

(3)热设计

下面是硬件工程师和热工程师之间的一则笑话:

硬件工程师:“我们新出了一个方案,帮忙再仿真一下吧?”

热设计工程师:“过不了!”

硬件工程师:“你仿过了?”

热设计工程师:“我用脑袋仿过了,你过不了,你要降规格!”

硬件工程师:“我要用烙铁给你脑袋加加热。”

这个笑话现在已经在网上广为流传,但这个笑话却是我亲身经历的真实事件。

当时我刚到华为上班,意气奋发,希望项目尽快取得进展,结果就碰到这么一个不配合我们项目组工作的热设计工程师,还很不理解他的工作态度。

因为即使是大公司,专门搞热仿真热设计的从业人口也比较少,特别是华为这个专门的工作,只有热设计工程师才可以使用仿真软件。所以当时热设计工程师是稀缺资源,硬件工程师也只能依赖热设计工程师进行仿真。

而很多公司热仿真的工作是结构工程师完成的。也有些能干的硬件工程师自己建模仿真。这个取决于个人的技术宽度、公司的分工要求、产品复杂度、必要性等。

不管是什么工程师来做这个工作,如果反复的仿真没有好的结论,都是资源浪费。自然就会有笑话中热设计工程师拒绝反复仿真各种情况的案例。

我们在硬件设计过程中,由于芯片的性能越来越高,接口的速率越来越高,各种芯片的热耗也随之增大,所以热设计的挑战也越来越大。特别是产品竞争进入白热化之后,在有限的机框里面达到散热极限边缘是很容易出现的。

热仿真效率低的原因有:

① 器件功耗大,散热风险大。

② 热设计仿真结果经常超过结温,或者不满足降额。

③ 有些给出的器件功耗值缺乏理论依据,不准确,导致过设计或者导致散热风险。

④ 热仿真的过程需要多次反复,一次仿真的周期大约3天,效率低下。

有时候硬件工程师按照项目经验经过多次调整,才能满足热设计的要求,而且不断的改热设计的输入条件,导致效率很低。

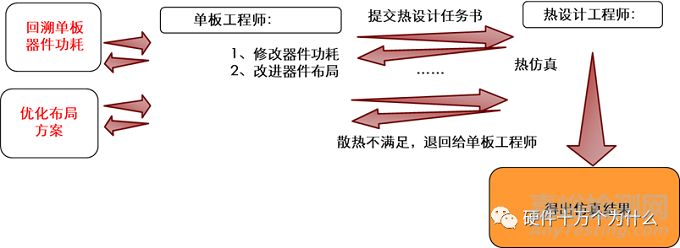

预布局、结构设计、热设计的关系和流程如下图所示。

布局、结构设计和热设计流程

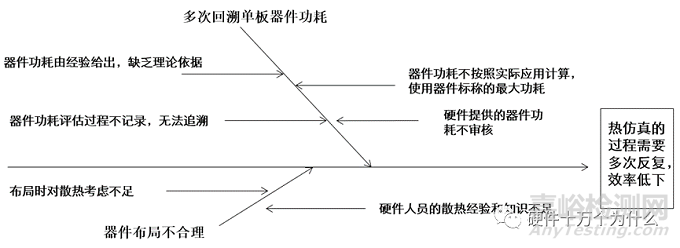

分析之前的流程,热仿真效率低的原因如图所示。

热仿真效率低的原因分析

对于风险器件,我们需要做到两点:

(1)准确给出器件实际功耗。

(2)最优化的散热布局,考虑走线的前提的下的最优布局。

关于器件功耗评估,对于没有散热风险的器件,我们评估功耗的时候,可以很粗暴地给一个标称最大值。但是当这样简单操作,给出一个最大值之后,不能通过热仿真的时候,需要我们去调整这个值,需要评估到最准确的值。

(1)例如,DDR3控制器支持高刷新率,则其结温可达到95℃,如果不支持高刷新率,则最高结温定为85℃。必要时,硬件实现提高刷新频率功能,则DDR3温度规格放宽为95度。其他器件如果有硬件指标跟温度相关,一样要根据实际需求和实际场景去评估其温度上限要求。

(2)对于散热风险较小的仿真模型,可以建立简单的电源模型,按照经验值输入。对于设计风险较大单板,需要建立电源详细模型,硬件人员需要提前评估功耗,提供给热设计人员。特别是MOSFET,有时候为了简化模型,直接布放一个热源,进行仿真。但是由于功耗大,所以我们要根据MOSFET的实际使用情况,利用功耗计算公式,计算出其实际的功耗,然后再确定其功耗参数。同时,需要考虑一些覆铜,亮铜改善其散热的情况。而不是简单的降规格妥协,或者换更贵更好性能的器件,要么影响产品竞争力,要么提升了成本。

(3)CPU的功耗要根据其是否降频工作,超频工作,实际工作负载情况进行评估。不能拿最大功耗一刀切。X86处理如果支持Turbo Burst模式,需要考虑多种情况的散热分析。由于Nehalem架构处理支持TurboBurst模式,所以虽然处理的总功耗一定,但是处理各个点的功耗会随着不同的Turbo模式,导致各个Core的最大功耗会超过其额定功耗。需要分别考虑各种情况的散热。不然超频的时候,单点功耗会比较高。

我们曾经有个案例,使用多核PowerPC,其功耗比较高,热仿真一直评估有风险,但是我们根据实际业务场景,重新评估了实际工作负载能力,合理的评估了其真实环境下的实际工作功耗,降低功耗之后仿真通过。后来实测,也不会出现过温的现象。对于处理器这种,需要的时候,应该投入人力,用demo板对实际工作环境进行实测,提前做热测试,保障功耗评估准确。同样的,DDR也需要根据其实际工作速率进行评估其功耗,特别是FPGA的外挂DDR,有时没有想象的那么大功耗。

(4)FPGA 的功耗,一般厂家会提供评估工具。这时,一定要根据实际FPGA的资源占有情况进行评估,不要按照100%进行评估。实在评估值偏高,也可以用Demo板实测功耗。

关于热设计相关的PCB布局、结构设计、生产工艺的几条经验。

(1)共用散热器,需要考虑器件公差及导热硅胶的厚度。

当时有个案例,我们有一个电路板上面,CPU和另外一个器件共用了散热器,自己公司的热设计工程师的仿真结论温度比较高,而使用相同的仿真模型,器件厂家散热仿真模型的温度比较低,经过器件厂家讨论,分析原因是器件厂家建立的仿真模型,CPU与散热器的导热胶厚度为0.13mm,而我们目前仿真模型中使用的仿真模型是0.3mm。导致:器件厂家仿真模型中CPU的温度是95摄氏度,而我们的仿真结果是:大于116摄氏度。自己公司的热设计工程师选择0.3mm是参考两个器件公差,得出的经验值,选取了概率比较高的一个参考值。

实际生产过程中,导热硅胶的厚度很难控制那么精准,需要制造特殊的涂胶工装来保证其厚度。不然确实会出现大功率器件温度过高,出现过热保护的情况。建议最好不要多个器件共用散热器。由于器件高度公差,导致导热硅胶厚度影响散热效果。如果多个器件共用散热器,需要充分考虑器件高度公差带来的影响。

(2)有些场景下,DDR在正反面,为了方便走线,有些工程师把TOP面和BOTTOM面的DDR在空间上位置完全重叠。但是这样重叠设计,DDR的热量也会通过PCB板相互传递,不利于散热,可以考虑错开一点进行设计。在指标就差一点点的时候,这种设计能够有效地优化。

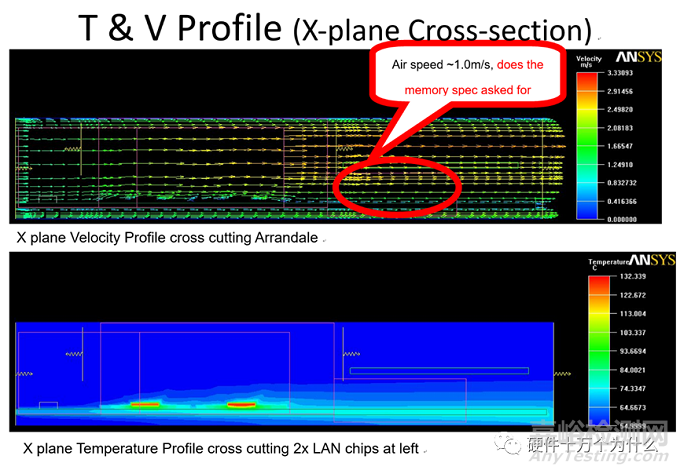

(3)散热器件后方如果有扣板等平板型物体,不一定会阻碍器件散热,有可能形成风道,加大局部风速。有时风道会改善散热,所以不要拿脑袋仿真。热仿真图如图5.17所示。

热仿真图

(4)散热有叠加效应。如果存在很大散热风险,优先考虑将结温要求最苛刻、功耗大的器件放在进风口。例如DDR。

(5)过孔、亮铜会改善散热。

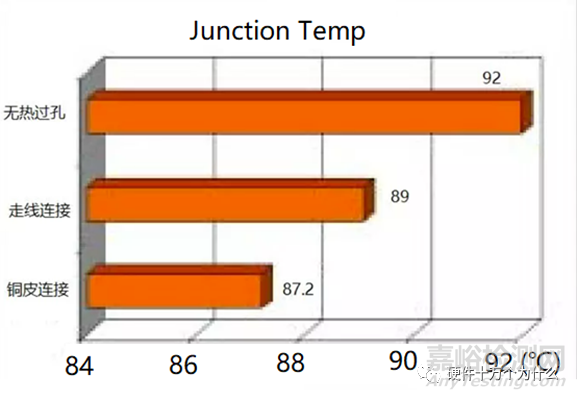

(6)加散热铜箔和采用大面积电源地铜箔。连接方式与结温的关系如图5.18所示。

连接方式对结温的影响

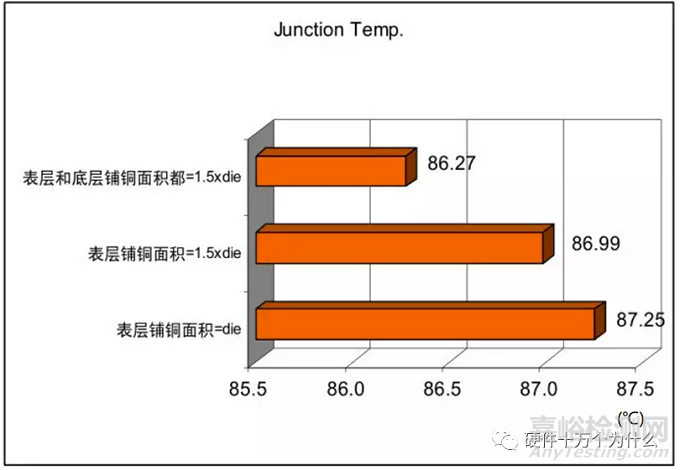

根据上图可以看到:连接铜皮的面积越大,结温越低。铺铜面积与结温的关系

铺铜大小对结温的影响

根据上图,可以看出,覆铜面积越大,结温越低。

来源:硬件十万个为什么