您当前的位置:检测资讯 > 科研开发

嘉峪检测网 2022-07-26 21:53

静电不可捉摸,却又无处不在。人们只有深刻认识到静电的危害和影响机理,并在各个相关环节采取有效的静电防护措施才能防范并降低电子产品的ESD失效风险。

一、半导体的ESD失效模式

电子产品因ESD可能引起半导体元器件损伤而导致失效或故障。半导体器件的静电损伤,有两类模式,即突发性完全失效和潜在性损伤。

ESD使元器件突发性完全失效的概率仅约10%,表现为短路、开路、无功能、参数不符合要求等;而90%情况下则是元器件遭受到潜在性轻微损伤,损伤后电参数仍能符合规定的使用要求,但减弱了元器件抗过电应力(EOS)的能力,在使用现场容易出现早期失效。

1.1突发性完全失效

突发性完全失效是器件的一个或多个电参数突然劣化,完全失去规定功能的一种失效。通常表现为开路、短路以及电参数严重漂移。

半导体器件ESD损伤失效现象主要包括:

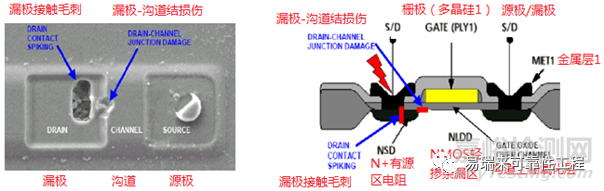

介质击穿

图1. 介质击穿

铝互连线损伤与烧熔

硅片局部区域熔化

图2. 硅半导体热熔-铝线热熔

PN结损伤和热破坏短路

扩散电阻与多晶电阻损伤

ESD可触发CMOS集成电路内部寄生的可控硅(SCR)“闩锁“(Latch-up)效应,导致器件被过大电流烧毁。

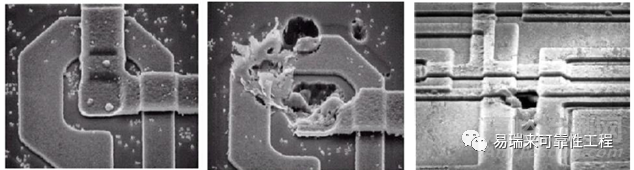

对微电路中的一段线路做ESD实验发现:

①200V~400V时 线路的阻抗没有发现变化

②600V时 微电路的性能指标稍有下降,但仍能通过测试。

③800V~900V 出现了局部熔断和孔洞,线路阻抗发生了明显变化

④1000V 线路断开,器件被完全损坏

图3. 微电路ESD试验

1.2潜在性损伤

如果带电体的静电势或存储的静电能量较低,或ESD回路有限流电阻存在,一次ESD脉冲不足以引起器件发生突发性完全失效,但它会在器件内部造成轻微损伤,这种损伤又是积累性的。随着ESD脉冲次数增加,器件的损伤阈值电压逐渐下降,器件的电参数逐渐劣化,这类失效称为潜在性失效。潜在性失效的表现往往是器件的使用寿命缩短,或者一个本来不会使器件损伤的小脉冲却使该器件失效。潜在性失效降低了器件抗静电的能力,降低了器件的使用可靠性。半导体器件潜在性失效主要表现为:

(1)栅氧化层损伤

MOS栅氧化层受到ESD的作用,会产生细微损伤,有时会导致栅极泄漏电流少量增加。这种情况的发生可能是由于放电时形成丝状铝硅合金,该合金尚不能跨接整个栅氧化物,使得受损的氧化层击穿电压降低,在使用时就可能由于低能量EOS或者ESD使得已经受损的氧化层击穿,从而使器件失效。栅氧化层的击穿机理,目前认为可分为两个阶段:

第一阶段是建立阶段,或称为磨损阶段。在电应力作用下,氧化层内部及Si-SiO2界面处发生缺陷(陷阱、电荷)的积累,积累的缺陷达到某一程度后,使局部区域的电场(或缺陷数)达到某一临界值,转入下一阶段:

第二阶段是在热、电正反馈作用下,迅速使氧化层击穿的过程。栅氧寿命主要由第一阶段中的建立时间所决定。对电应力下氧化层中及界面处产生的缺陷,一般多认为是电荷引起的,对电荷的性质,主要有二种理论模型:负电荷积累模型和正电荷积累模型(此处不作详细说明)。

(2)栅氧化物愈合/短路

形成的丝状铝硅合金也可能在后续的静电放电作用下被烧毁,从而使氧化栅得到“自愈”。但“自愈”的氧化栅会由于不可靠而降级,它会在后续的工作中遇到过应力或是低能量的ESD脉冲时,容易使缺陷扩大或使氧化栅发生短路。

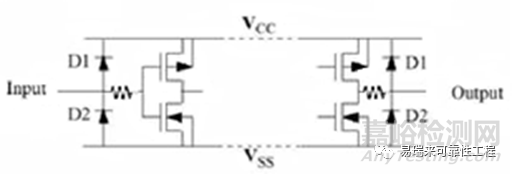

(3)内部保护电路受损

集成电路内部通常设计了ESD保护电路。常见的CMOS器件内部电应力保护电路单元有:电阻、二极管、MOS管、SCR等。器件内部的电应力保护网络通常由这几个保护电路单元的一种或者多种组合构成,具体的选择应根据电路参数、工艺类型和版图设计的实际情况决定。

图4. 器件内部的ESD保护电路

当起保护作用的二极管受到破坏,其I-V特性曲线变坏,在电流的传输过程中产生时间延迟效应,波形的时间延迟会使器件产生细微的损伤。

(4) 电荷陷阱

静电放电产生的高压瞬时脉冲会破坏器件上的电荷平衡,从而形成电荷陷阱。大量的电荷积聚在器件表面形成反型层,该反型层提供了电流泄漏通路,反型层泄漏是一个与时间和温度有关的退化现象,它会导致器件完全失效。

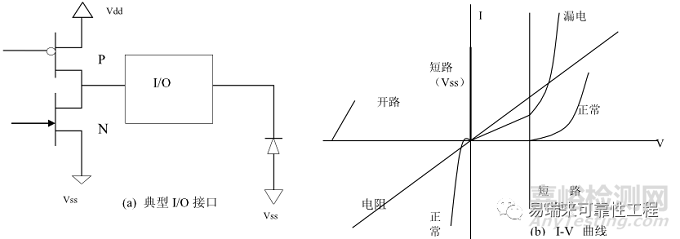

(5) PN结衰减

通过观察硅PN结的I-V特性曲线就可以发现它是否已经损伤。瞬时的局部加热或电应力都会使铝硅合金丝状化,这些丝状物构成了一个并行分流器,在反偏I-V特性曲线上形成一个尖锐的拐点。铝硅合金熔融需要很高的温度。在ESD引起损伤的事件中,PN结丝状横截面积变得很小,以至于在使用过程中产生局部加热,从而导致失效。静电放电熔断如此小的细丝是非常可能的,从而使器件虽然可以使用但却不再可靠。

图5. 典型I/O电路及其I-V曲线

二、半导体的ESD失效机理

半导体器件的静电损伤,其失效机理可分为两类:一类是与电流有关的失效,如PN结的损伤,接触孔合金钉,金属/多晶硅互连线或电阻烧坏;另一类是与电压有关的失效,ESD引起栅氧化层击穿是最常见的电压型失效。

2.1电流型损伤机理

(1) PN结的损伤和接触孔合金钉

ESD引起PN结短路是最常见的失效现象。当PN结(尤其是浅PN结,如双极型晶体管的发射结或NMOS管的漏极与衬底间的结)发生雪崩击穿,再进一步发展为二次击穿时,瞬态大电流产生的焦耳热导致局部温度急剧上升,这一局部的热量 又会加速热载流子的产生,大量产生的热载流子又会进步增大瞬态大电流, 最后导致局部温度超过1415摄氏度而发生硅的熔化,引起合金钉穿透PN结而失效。如果产生的热量足够熔化邻近接触孔的金属,熔化的金属会在电场的作用下在结间迁移,导致结间的电阻型短路。当位于PN结二次击穿点处的熔化的硅发生再凝固时,PN结处的P型和N型掺杂剂的分布发生了改变。而且,再分布的过程改变了硅的晶体性质。这些变化导致结间反向漏电流小幅或大幅增加。版图设计对PN结短路有很大影响,最敏感的是接触孔尺寸、形状及位置。较好的办法是在一个扩散区内设置多个小接触孔,以便增加孔周长:用圆形接触孔可避免电流的非均匀流动:增加接触孔与扩散区的间距,可防止电流在接触孔角落处集中。

(2) 金属/多晶硅互连线或电阻烧坏

ESD事件产生的局部焦耳热也可能使金属/多晶硅互连线或电阻烧坏,这主要取决于铝线或多晶硅线的宽度、接触孔尺寸、结面积和电流分布等。互连线的电流携带能力是它的横截面积的函数,并且还与电流聚集、台阶覆盖和热阱等因数有关。例如由于氧化层台阶处的铝层横截面积的减小,在ESD脉冲的大电流作用下,铝层更容易熔化而开路,导致器件的功能失效。ESD脉冲大电流有时只是部分熔化电阻材料,导致电阻值的漂移和相关器件电参数的失效。当输入ESD保护电路中有多晶硅电阻时,静电放电容易使多晶硅电阻受到损伤,失效部位常出现于多晶硅电阻拐弯处和多晶硅电阻与铝互连线的接触孔处。扩散电阻的抗静电能力明显好于多晶硅电阻,这是因为扩散电阻的衬底可充当为一个有效的热阱,而多晶硅电阻周围的介质氧化层却阻碍了多晶硅电阻的散热。互连线承受大电流能力依赖它的横截面积,因此输入保护结构应尽量靠近键合焊盘(PAD)以缩短铝互连线长度,铝互连走线应做得足够宽,以提高抗电过应力的能力。电阻抗电过应力的的能力取决于其端头、接触孔的大小以及电阻条宽与长度。

2.2电压型损伤机理

(1)栅氧化层损伤

当半导体器件遭受极短上升时间的ESD脉冲时(如带电器件模型),ESD保护器件还未作出及时反应,ESD 电压就直接加到处在ESD保护器件下一级的MOS器件的栅极上,导致栅氧化层损伤。栅氧化层击穿是最常见的过电压场致失效。过高的ESD电压可能使介质层损伤,其损伤过程可分成以下三个阶段。首先,在介质层的某个高电场点(如介质层的边角和台阶处),ESD脉冲产生的高压超过了介质的绝缘强度;其次,介质击穿形成的大电流流过击穿点,产生相邻区域的热斑;最后,局部的高温熔化了多晶硅栅,形成多晶硅熔化丝状物,或者,当栅氧化层由于制造工艺缺陷而有针孔时,ESD电压会使得击穿首先在针孔处发生。

(2)铝互连线与扩散区短路

短路常发生在键合焊盘(PAD)连接的扩散电阻和横跨其上的电源铝条之间。由于它们之间是热氧化层且厚度较厚,所以这种短路失效几率比较小。

(3)铝互连线与多晶电阻短路

短路常发生在键合焊盘(PAD)连接的多晶电阻和横跨其上的电源或地互连线之间。由于铝互连线与多晶硅电阻之间介质击穿强度比热氧化层低得多,当输入端引入ESD时可导致该处介质击穿短路,因此版图设计时输入端的多晶硅电阻条与铝条之间应留足够距离,更要防止多晶硅电阻条与铝条重叠。

三、如何防范ESD对半导体的损伤

解决问题的不二法则,一方面加强自身的防护能力(内因);另一方面管控静电产生、积累和泄放的所有场景(外因)。

因此,在设计芯片时必须提升芯片自身的ESD防护能力,尤其对于外部接口类器件。但随着集成电路的集成度越来越高,在芯片内部设计防护电路的成本也越来越高,甚至由于半导体工艺限制和信号特性的要求,难以在芯片内部增加防护电路,这就要求在使用芯片进行应用电路设计时,一定要充分考虑元器件、电路板、整机的ESD防护。

另外,从芯片本身的半导体制程中以及电路板PCBA的全生产过程中务必加强从人、机、料、法、环等各个方面对ESD进行管控,减少静电来源,并使静电能以安全方式和通路泄放掉,不会直接作用到器件引脚上。

来源:易瑞来可靠性工程