您当前的位置:检测资讯 > 科研开发

嘉峪检测网 2018-02-07 09:36

随着电子技术的飞速发展,电子产品正朝着微型化、轻便化、多功能化、高集成化和高可靠性方向发展,而半导体器件的封装也正朝着多引脚、细间距和表面贴装的方向发展。相应地,作为各种元器件的支撑和互连的 PCB 则正朝着小型、高速、高密度和轻量化的方向不断攀升,其设计的复杂程度带来的各种挑战不断增加,厂商面临的产品面世时间的压力也越来越大。在信号完整性分析研究的同时,如何 提供稳定可靠的电源也已成为重点研究方向之一。 尤其当开关器件数目不断增加,电源电压不断降低 的时候,电源电压和地电位的波动会给高速系统带来致命的影响。随着高速系统设计对仿真精度要求的提高,简单的假设电源电压和地电位绝对处于稳定状态,已越来越不能被接受。于是电源完整性的分析研究应运而生。

高速 PCB 的信号完整性技术经过几十年的发展,其理论、分析方法和实践都已比较成熟。但电源完整性是一项新的技术,目前它是高速PCB 设计最大的挑战之一。

1、电源完整性概念

电源完整性这一概念是以信号完整性为基础的,两者的出现都源自电路开关速度的提高。当高速信号的翻转时间和系统的时钟周期可以相比时,具有分布参数的信号传输线、电源和地就与低速系统中的情况完全不同了。与信号完整性是指信号在传输线上的质量相对应,电源完整性是指高速 电路系统中电源和地的质量。它在对高速电路进行仿真时,往往会因信号参考层的不完整造成信号回流路径变化多端,从而引起信号质量变差和产品的EM I性能变差,并直接影响信号完整性。

电源完整性问题是指在高速系统中,电源分配网络在不同频率时,存在不同输入阻抗,导致 PCB电源 /地平面上出现由△I噪声电流、瞬态负载电流引起 的△I 噪声 电压 ,造成供电不连续,产生 电磁骚扰发射,严重影响高速系统的正常工作。

当前,电源完整性 问题主要通过两个途径解决,即优化 PCB 的叠层设计及布局布线和安装去耦 电容。在高速系统工作速率低于400M H z,在恰当位置安装合适的去耦电容,有助于减小电源完整性问题;当系统速率更高时,去耦电容作用减小。这时,只有通过优化 PCB 层间距设计及布局布线,降低电源电压,以及适当匹配、降低反射等办法解决电源完整|』 生问题。完全解决电源完整性问题,难度比解决信号完整性问题更大,对工程师的技能要求更高。

2、电源完整性仿真分析

2.1采用等效输入输出电阻仿真

在实际的电路设计中,可能因为电路太复杂,可以使用这种方法,比较简便地估计芯片的 SSN 噪声,速度快,节省资源,但是精度不够。

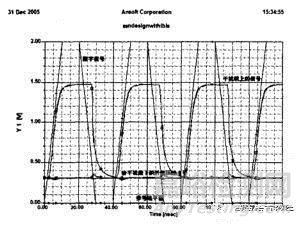

由于驱动的低输出阻抗和接受端高的输入阻抗,可以用 2f/和 200f/的电阻近似等效驱动端和接受端的阻抗,板子电源电压为 3.3V ,两个干扰线加 同相信号,如 图一所示 。

图一 仿真原理图

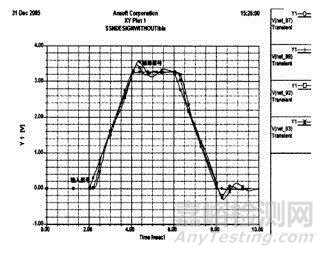

图二 干扰线上的输入输出信号

(a)电源电压波动 (b)被干扰线上电压波动

图三 电源和被干扰线上的信号

图二是干扰线两端的信号波形,图三为电源和被干扰线两端的电压波形。从其中可以看 出,静态线即被干扰线上不是保持零电平,它受板子电源 /地电压差值和附近其它干扰线的影响,电压产生波动。电源上的波动小于 140m V ,被干扰线上 的电压波动小于 3m V 。

2.2 采用 IBIS 模型仿真

在实际的设计当中,一些厂家会给出IBIS 模型。应用这些模型,可以很准确地仿真芯片管脚的电压值,仿真出来的结果也更接近真实值,我们可以很方便地应用这些IB IS 来协助我们的设计。

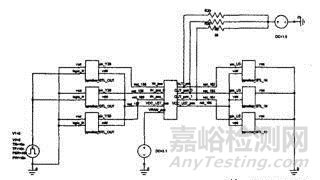

带有IBIS模型的电路仿真原理图如图四所示。仿真采用Nexxim仿真器,用Designer导入ibs文件,这里的输出和输入ibs模型选用GTL-OUT和GTL-IN模型。这个IBIS模型规定逻“0”电平大约为0.3V,逻辑‘1’电平大约为1.5V,输出必须接一偏置电压,即通过一个25欧的电阻链接到1.5V的电压源,输入激励如图五所示。

图四仿真原理图

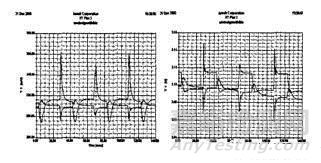

图五 输入理想信号和输出管脚信号

图五为两芯片管脚电压,图六为静态线上电压 波形和电源电压的噪声仿真结果。从图六(右)可以看出,电源噪声小于 100m V 。依照以上的方法,可以对板上各个芯片进行仿真,确定他们的SSN,从而进一步确认他们的工作状态。

图六 被干扰线上的信号电压和电源线上的电压

3、结束语

高速电路的 PCB 板级设计是十分具有挑战性的。为了保证电路的正确工作,需要精心设计电路的PDS,包括在电路板上添加数以百计的退耦电容,并且根据需要选择合适的电容值及其位置。采用仿真的方法替代反复试验的设计方法来优化电路板的电源完整性设计,可以有效缩短设计周期并且节约设计成本。

来源:AnyTesting